P90X0 MVME141 32bit VME bus Microcomputer

**Field Support Manual**

ADDS

РН

NEW

DIMENSIONSTO

CUS

OMER

SERVICE

P90X0 MVME141 32bit VME bus Microcomputer

2

Field Support Manual

A Publication of PHILIPS TELECOMMUNICATIE EN DATA SYSTEMEN NEDERLAND B.V. Customer Service Documentation and Training Apeldoorn, The Netherlands

Pub. No. 5122 991 37681

Date January 1989

Great care has been taken to ensure that the information contained in this handbook is accurate and complete. Should any errors or omissions be discovered or should any user wish to make a suggestion for improving this handbook, he is invited to send the relevant details to:

PHILIPS TELECOMMUNICATIE EN DATA SYSTEMEN Customer Service Documentation and Training P.O. BOX 245 7300 AE APELDOORN THE NETHERLANDS

## STATUS RECORD

TITLE :

P90X0 MVME141 32bit VME bus Microcomputer Field Support Manual

PUBLICATION NUMBER : 5122 991 3768X

| x | UPD. | SI No. | PAGES AFFECTED | DATE | REMARKS                |

|---|------|--------|----------------|------|------------------------|

|   |      |        | All            | 8901 | First Issue MVME141/D1 |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        | -              |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                | -    |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

|   |      |        |                |      |                        |

## Preface

This manual provides general information, hardware preparation, installation instructions, functional description, and support information for the MVME141 32-Bit VMEbus / VBS-based microcomputer.

This manual is intended for anyone who wants to design OEM systems, supply additional capability to an existing compatible system or in a lab environment for experimental purposes.

A basic knowledge of computers and digital logic is assumed.

To use this manual, you should be faimilar with the publications listed in the *Related Documentation* paragraph in Chapter 1 of this manual.

The information in this document about the VME141 module jumper setting is not explicit for the P90X0 configuration.

To be sure having the correct jumper setting, refer to the Customer Engineer Manual P90X0 or to the Installation Instructions delivered with the VME141 board.

The part numbers in the section 5.3 are the Motorola part numbers. These numbers can be out of date.

For the correct numbers see the Spare Parts P90X0 manual distributed by Customer Service logistics.

A copy of the current list containing the MVME141 related items is included at the end of this manual.

The computer programs stored in the read only memories of this device contain material copyrighted by Motorola, Inc., first published 1988, and may be used only under a license such as the License for Computer Programs (Article 14) contained in Motorola's Terms and Conditions of Sale, Rev. 1/79.

## WARNING

THIS EQUIPMENT GENERATES, USES, AND CAN RADIATE RADIO FREQUENCY ENERGY AND IF NOT INSTALLED AND USED IN ACCORDANCE WITH THE INSTRUCTIONS MANUAL, MAY CAUSE INTERFERENCE TO RADIO COMMUNICATIONS. IT HAS BEEN TESTED AND FOUND TO COMPLY WITH THE LIMITS FOR A CLASS A COMPUTING DEVICE PURSUANT TO SUBPART J OF PART 15 OF FCC RULES, WHICH ARE DESIGNED TO PROVIDE REASONABLE PROTECTION AGAINST SUCH INTERFERENCE WHEN OPERATED IN A COMMERCIAL ENVIRONMENT. OPERATION OF THIS EQUIPMENT IN A RESIDENTIAL AREA IS LIKELY TO CAUSE INTERFERENCE IN WHICH CASE THE USER, AT HIS OWN EXPENSE, WILL BE REQUIRED TO TAKE WHATEVER MEASURES NECESSARY TO CORRECT THE INTERFERENCE.

VMEmodule, VSB, and 141bug are trademarks of Motorola, Inc.

First Edition Copyright 1988 by Motorola, Inc.

# SAFETY SUMMARY SAFETY DEPENDS ON YOU

The following general safety precautions must be observed during all phases of operation, service, and repair of this equipment. Failure to comply with these precautions or with specific warnings elsewhere in this manual violates safety standards of design, manufacture, and intended use of the equipment. Motorola inc. assumes no liability for the customer's failure to comply with these requirements. The safety precautions listed below represent warnings of certain dangers of which we are aware. You, as the user of the product, should follow these warnings and all other safety precautions necessary for the safe operation of the equipment in your operating environment.

### GROUND THE INSTRUMENT.

To minimize shock hazard, the equipment chassis and enclosure must be connected to an electrical ground. The equipment is supplied with a three-conductor ac power cable. The power cable must either be plugged into an approved three-contact electrical outlet or used with a three-contact to two-contact adapter, with the grounding wire (green) firmly connected to an electrical ground (safety ground) at the power outlet. The power jack and mating plug of the power cable meet International Electrotechnical Commission (IEC) safety standards.

#### DO NOT OPERATE IN AN EXPLOSIVE ATMOSPHERE.

Do not operate the equipment in the presence of flammable gases or fumes. Operation of any electrical equipment in such an environment constitutes a definite safety hazard.

## **KEEP AWAY FROM LIVE CIRCUITS.**

Operating personnel must not remove equipment covers. Only Factory Authorized Service Personnel or other qualified maintenance personnel may remove equipment covers for internal subassembly or component replacement or any internal adjustment. Do not replace components with power cable connected. Under certain conditions, dangerous voltages may exist even with the power cable removed. To avoid injuries, always disconnect power and discharge circuits before touching them.

## DO NOT SERVICE OR ADJUST ALONE.

Do not attempt internal service or adjustment unless another person, capable of rendering first aid and resuscitation, is present.

### USE CAUTION WHEN EXPOSING OR HANDLING THE CRT.

Breakage of the Cathode-Ray Tube (CRT) causes a high-velocity scattering of glass fragments (implosion). To prevent CRT implosion, avoid rough handling or jarring of the equipment. Handling of the CRT should be done only by qualified maintenance personnel using approved safety mask and gloves.

#### DO NOT SUBSTITUTE PARTS OR MODIFY EQUIPMENT.

Because of the danger of introducing additional hazards, do not install substitute parts or perform any unauthorized modification of the equipment. Contact Motorola Field Service Division for service and repair to ensure that safety features are maintained.

#### DANGEROUS PROCEDURE WARNINGS.

Warnings, such as the example below, precede potentially dangerous procedures throughout this manual. Instructions contained in the warnings must be followed. You should also employ all other safety precautions which you deem necessary for the operation of the equipment in your operating environment.

## WARNING

Dangerous voltages, capable of causing death, are present in this equipment. Use extreme caution when handling, testing, and adjusting.

## TABLE OF CONTENTS

| CHAPTER | 1.1<br>1.2<br>1.3<br>1<br>1.4<br>1.5                                      | INT<br>FEA<br>SPE<br>.3.1<br>.3.2<br>GEN<br>REF                                                                                            | RODUC<br>TURES<br>CIFIC<br>Cool                                | TION<br>ATIC<br>ing<br>Comp<br>DESC<br>E DO                                                                                     | NS<br>Requ<br>liar<br>RIPT<br>CUME                                                                                            | iren<br>ice<br>ION                                                                                  | nent                                                  | s                          | · · · · · · · · · · · · · · · · · · · | •  |                                       | •             | · ·                                   | •                |   | •••••••                               | •                       | $ \begin{array}{r} 1 - 1 \\ 1 - 1 \\ 1 - 1 \\ 1 - 2 \\ 1 - 3 \\ 1 - 4 \\ 1 - 4 \\ 1 - 7 \\ 1 - 7 \\ 1 - 7 \\ \end{array} $ |

|---------|---------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------------------------------------|----------------------------|---------------------------------------|----|---------------------------------------|---------------|---------------------------------------|------------------|---|---------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------|

| CHAPTER | 2.1<br>2.2<br>2.3<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2<br>2.2 | INTI<br>UNP/<br>HARI<br>.3.1<br>.3.2<br>.3.3<br>.3.4<br>.3.5<br>.3.6<br>.3.7<br>SYS<br>.4.1<br>.4.2<br>.4.3<br>.4.4<br>.4.5<br>.4.6<br>INS | RODUC<br>ACKIN<br>DWARE<br>VMEC<br>VMEC                        | TION<br>G IN<br>PRE<br>hip<br>us L<br>ral<br>hip<br>ware<br>Bus<br>JPPO<br>r Di<br>ndec<br>Cabl<br>Cycl<br>32 C<br>al D<br>TION | STRU<br>STRU<br>PARA<br>Cont<br>Cloc<br>ock<br>Purp<br>Jump<br>EPF<br>Term<br>RT<br>stri<br>ing<br>e St<br>ing<br>istr<br>iNS | CTIO<br>TION<br>TION<br>Sele<br>Sele<br>Oose<br>Oose<br>Oose<br>Oose<br>Oose<br>Oose<br>Oose<br>Oos | ONS<br>(J1)<br>lect<br>ct (<br>Jump<br>J7)<br>ion<br> | ) .<br>t (J<br>J3)<br>Ders | 2)<br>5 (J<br>                        | 6) | · · · · · · · · · · · · · · · · · · · |               |                                       |                  |   | · · · · · · · · · · · · · · · · · · · | • • • • • • • • • • • • | 2-5<br>2-5<br>2-6<br>2-7<br>2-7<br>2-7<br>2-8<br>2-8<br>2-8<br>2-8<br>2-9<br>2-10<br>2-10                                  |

| CHAPTER | 3.1<br>3.2<br>3<br>3<br>3.3<br>3.3<br>3<br>4 -<br>4.1<br>4.2              | INTF<br>LED<br>.2.1<br>.2.2<br>.2.3<br>PUSF<br>.3.1<br>.3.2<br>FUNCT<br>INTF<br>ADDF                                                       | RODUC<br>INDIC<br>FAIL<br>STAT<br>RUN<br>IBUTT<br>ABOR<br>RESE | TION<br>CATO<br>Ind<br>Indi<br>Indi<br>ON C<br>T Sw<br>T Sw<br>T Sw<br>L DE<br>TION<br>1AP                                      | RS<br>icat<br>icat<br>cato<br>ONTR<br>itch<br>itch<br>SCRI                                                                    | or (<br>or (D<br>OLS<br>(S1<br>(S2<br>PTIC                                                          | DS1)<br>DS2)<br>S3)<br>) .<br>) .                     | •                          | · · · · · · · · · · · · · · · · · · · | •  | • • • • • • •                         | • • • • • • • | · · · · · · · · · · · · · · · · · · · | ·<br>·<br>·<br>· | • | • • • • • • • •                       | •                       | 3 - 1 3 - 1 3 - 1 3 - 1 3 - 1 3 - 2 3 - 2 3 - 2 3 - 2 3 - 2 3 - 2 4 - 1 4 - 1 4 - 1                                        |

|         |                                                                           |                                                                                                                                            |                                                                |                                                                                                                                 |                                                                                                                               |                                                                                                     |                                                       |                            |                                       |    |                                       |               |                                       |                  |   |                                       |                         |                                                                                                                            |

Page

vii

# TABLE OF CONTENTS (cont.)

| <ul> <li>4.2.1.1 CPU Space Address Map</li> <li>4.2.2 EPROM</li></ul> |     |     |   |   |   |   | $\begin{array}{c} 4-6\\ 4-7\\ 4-7\\ 4-9\\ 4-15\\ 4-16\\ 4-17\\ 4-17\\ 4-17\\ 4-21\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 4-22\\ 3\\ 4-22\\ 4-22\\ 3\\ 4-22\\ 3\\ 4-23\\ 4-23\\ 4-23\\ 4-23\\ 4-23\\ 4-23\\ 3\\ 8\\ 4-29\\ 3\\ 8\\ 4-3\\ 3\\ 8\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\ 3\\$ |

|-----------------------------------------------------------------------|-----|-----|---|---|---|---|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CHAPTER 5 - SUPPORT INFORMATION                                       | • • |     | • | • | • | • | 5-1<br>5-1<br>5-1<br>5-1<br>5-14                                                                                                                                                                                                                                                                                                                                                       |

| APPENDIX A - VMEchip LCSR BIT ASSIGNMENTS                             |     |     |   |   |   |   | A-1                                                                                                                                                                                                                                                                                                                                                                                    |

| APPENDIX B - VMEchip GCSR BIT ASSIGNMENTS                             | •   | • • | • | • | • | • | B - 1                                                                                                                                                                                                                                                                                                                                                                                  |

| APPENDIX C - VSB CSR BIT ASSIGNMENTS                                  | •   |     |   |   |   |   | C - 1                                                                                                                                                                                                                                                                                                                                                                                  |

# TABLE OF CONTENTS (cont.)

# LIST OF ILLUSTRATIONS

| FIGURE 1-1. | MVME141 BLOCK DIAGRAM 1-7                                              |  |

|-------------|------------------------------------------------------------------------|--|

| FIGURE 2-1. | CONFIGURATION REFERENCE DRAWING 2-4                                    |  |

| FIGURE 4-1. | MVME141 SYSTEM ADDRESS MAP (WITH VSB BOUNCE         ENABLED)       4-4 |  |

| FIGURE 4-2. | MVME141 SYSTEM ADDRESS MAP (WITH VSB BOUNCEDISABLED)4-5                |  |

| FIGURE 4-3. | PI/T PORT (CSR) ASSIGNMENTS 4-9                                        |  |

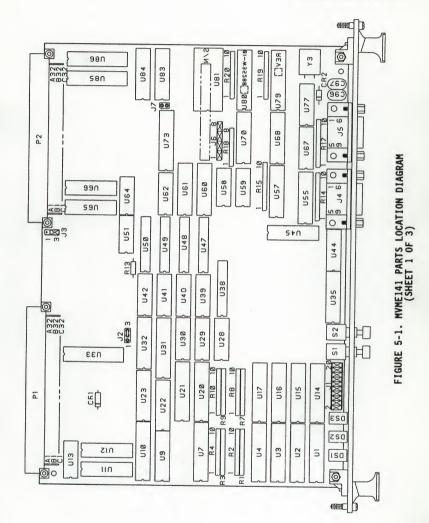

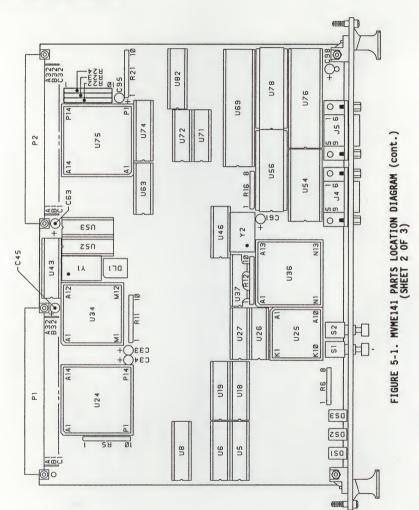

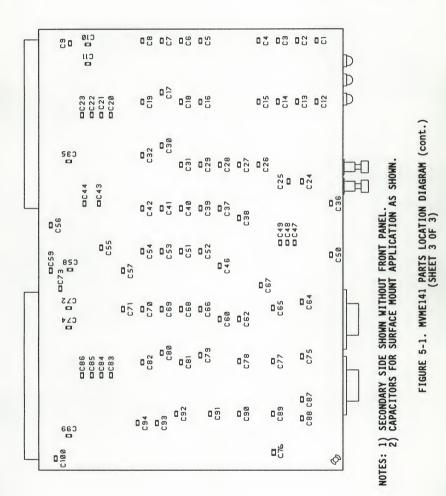

| FIGURE 5-1. | MVME141 PARTS LOCATION DIAGRAM 5-21                                    |  |

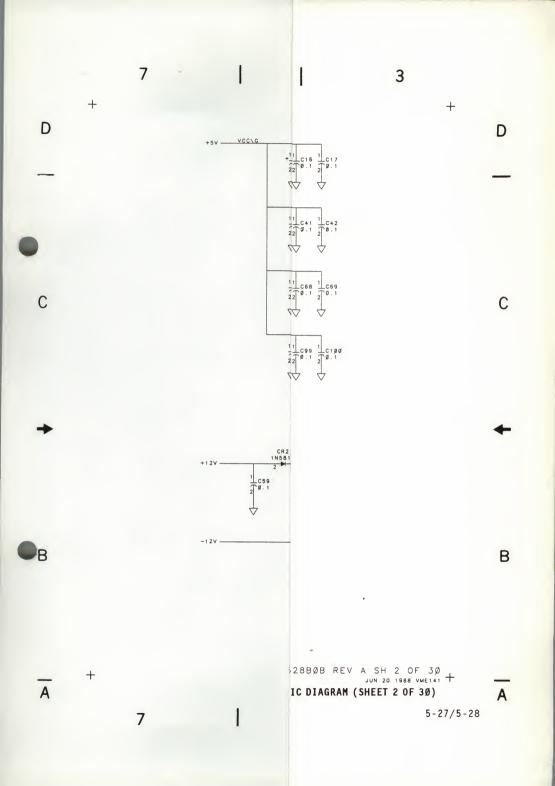

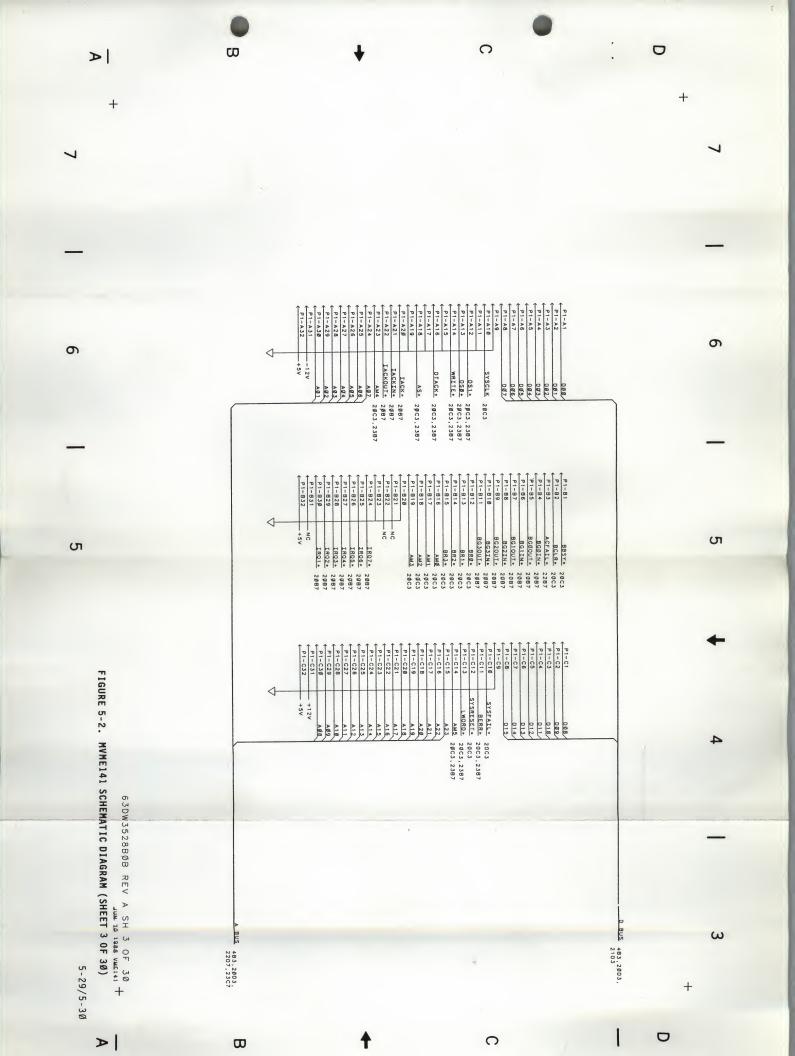

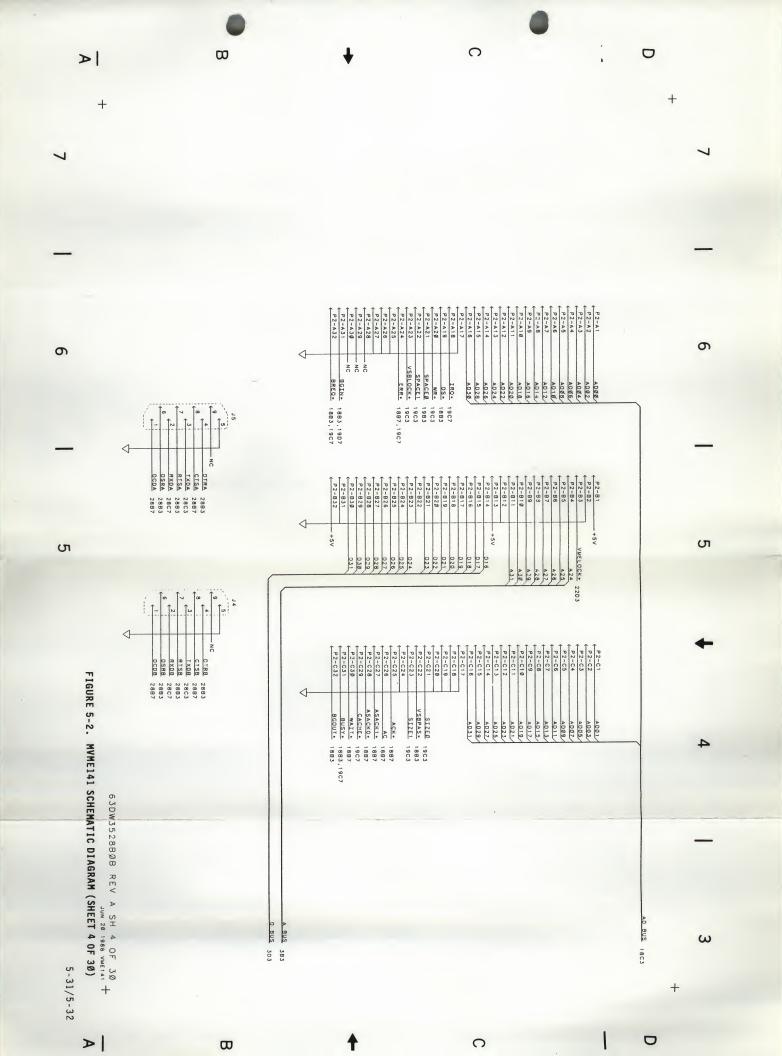

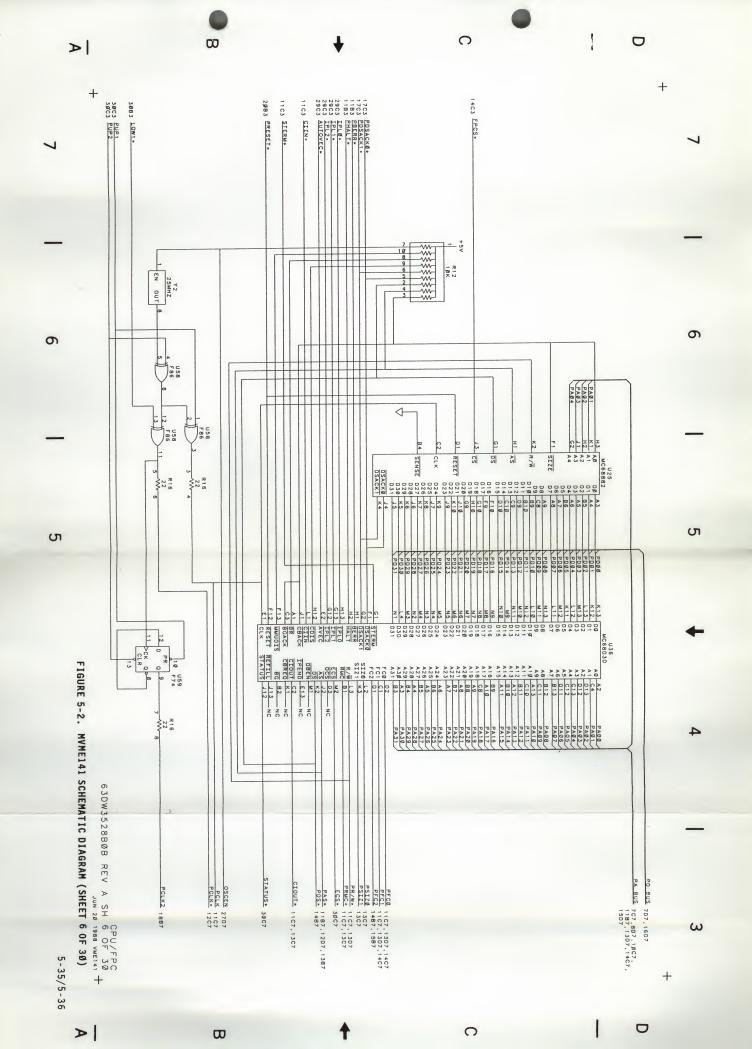

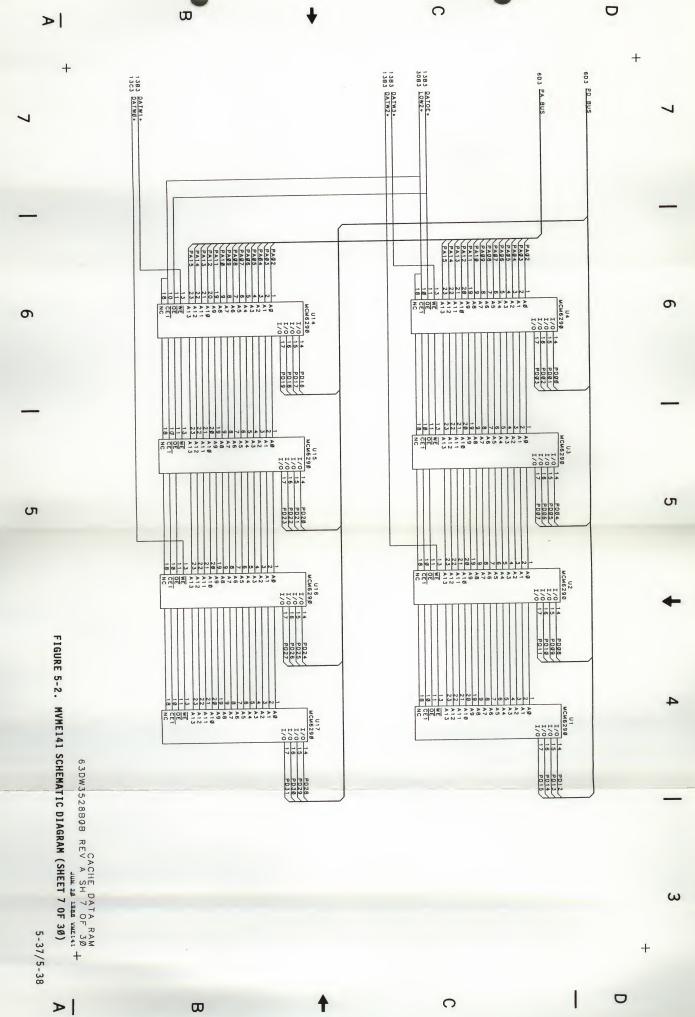

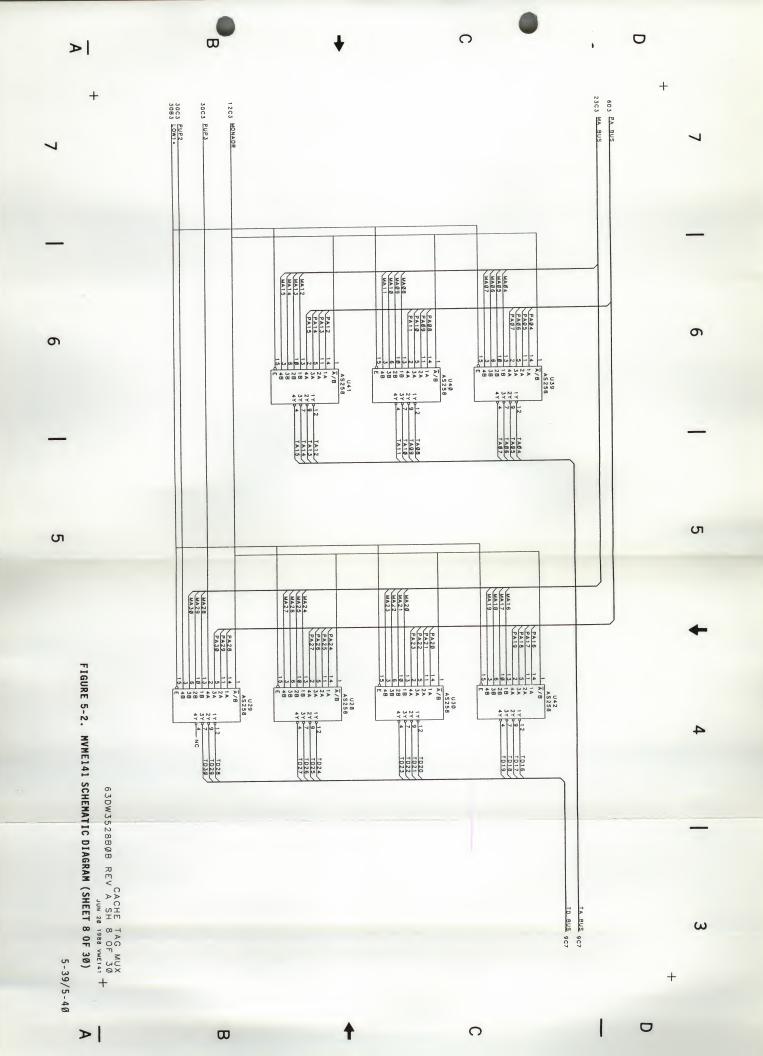

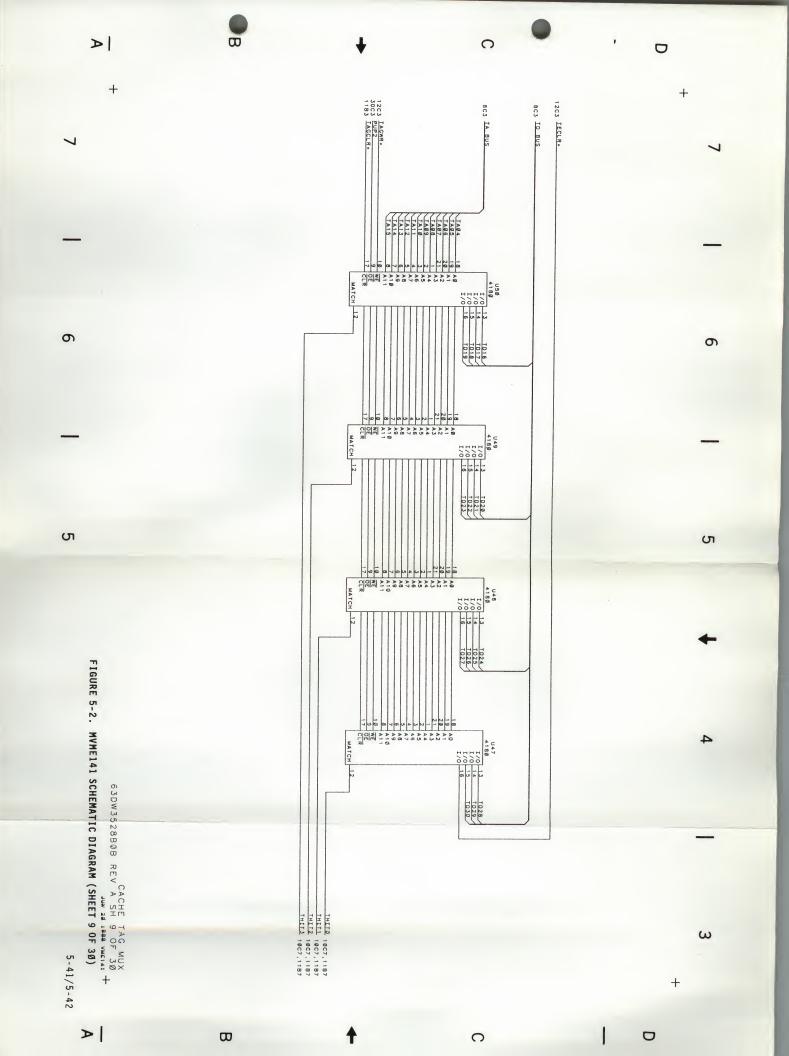

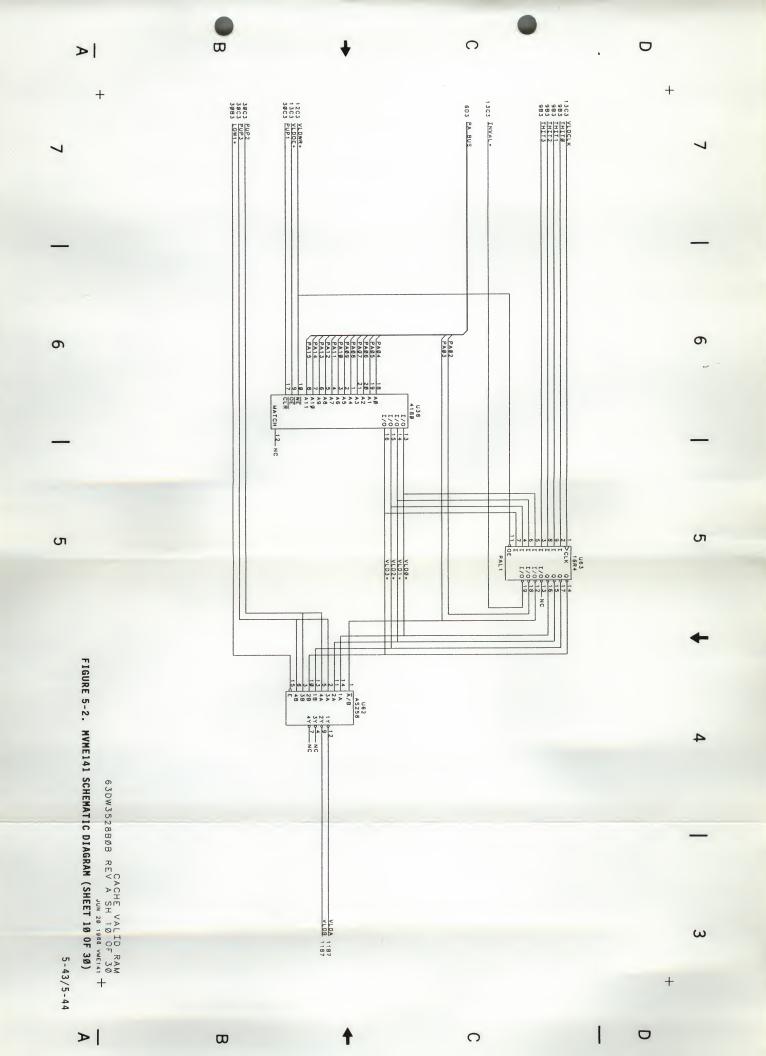

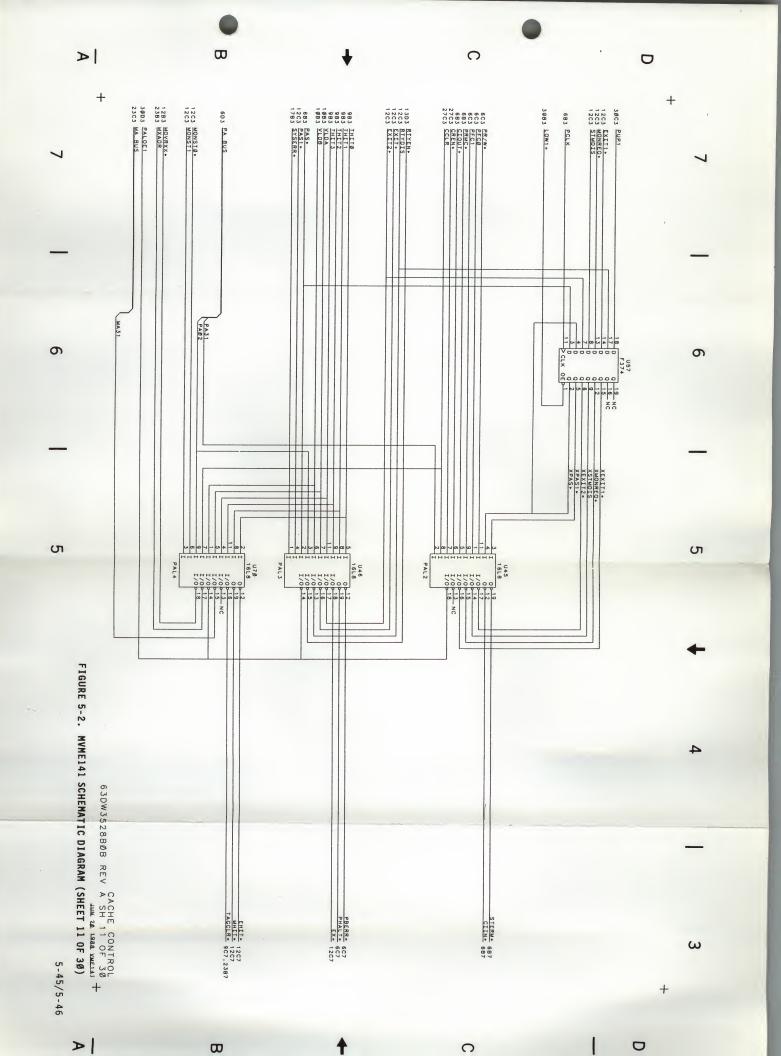

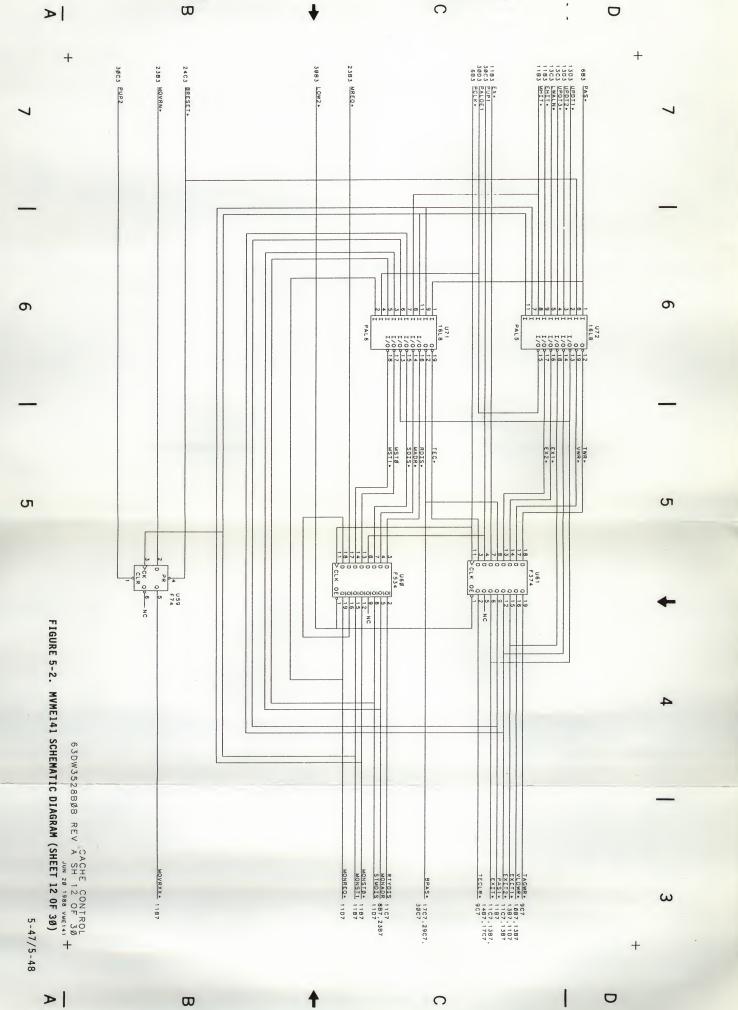

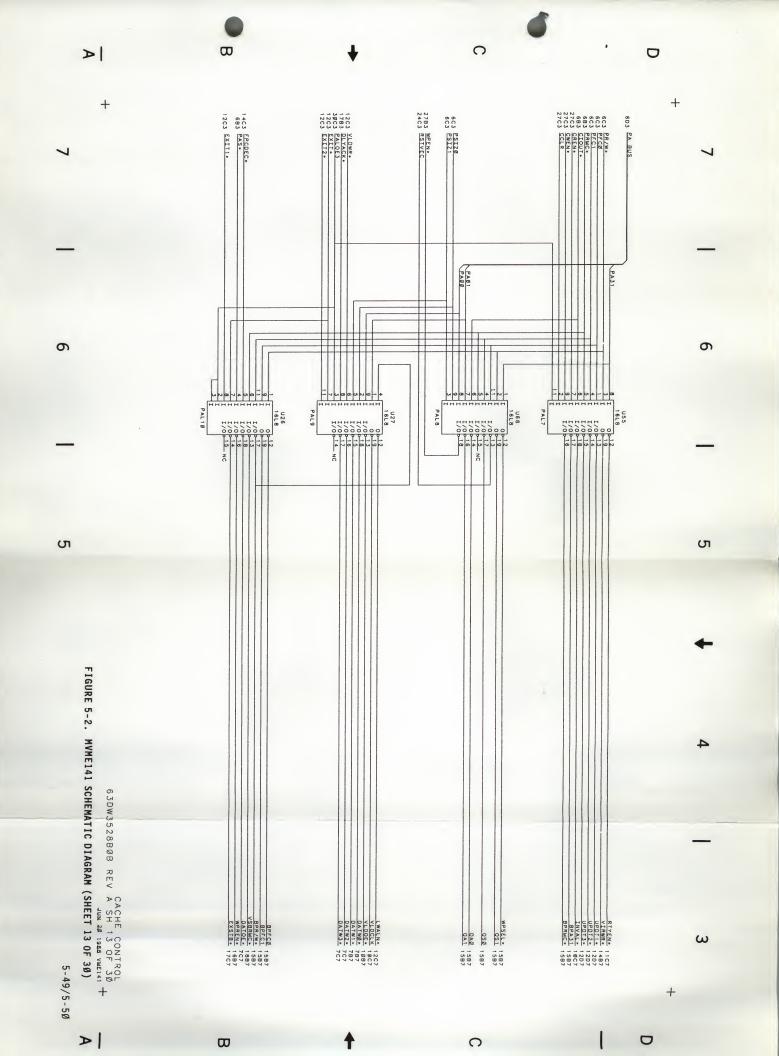

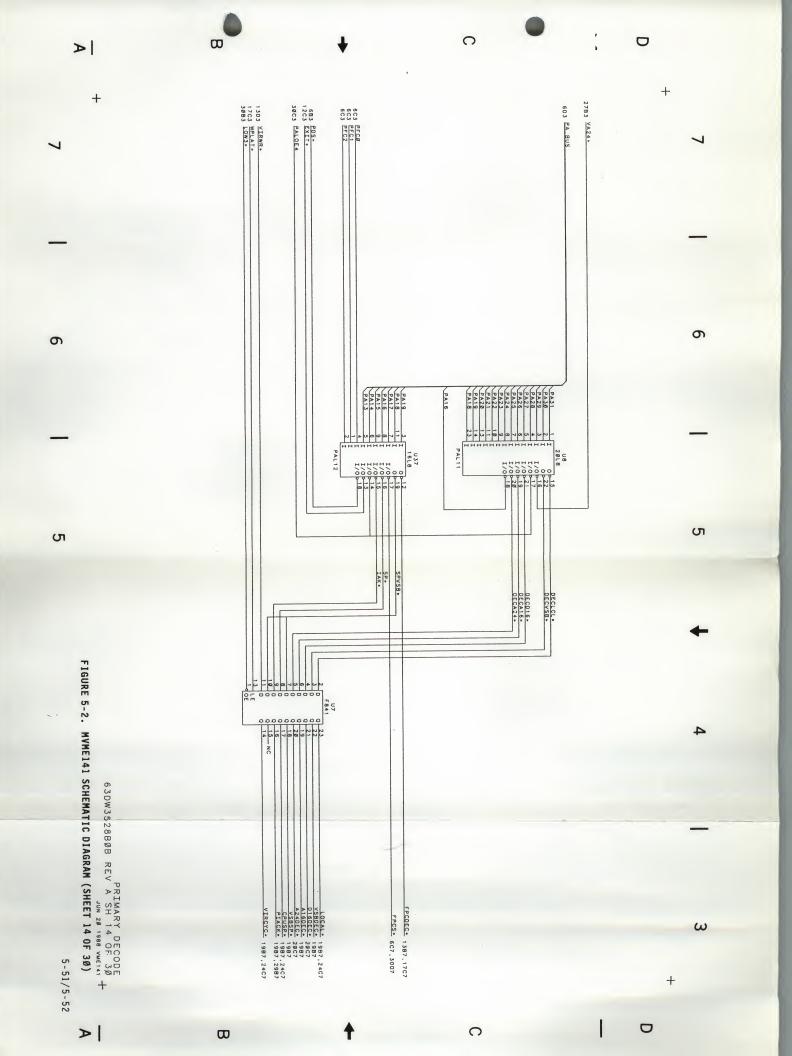

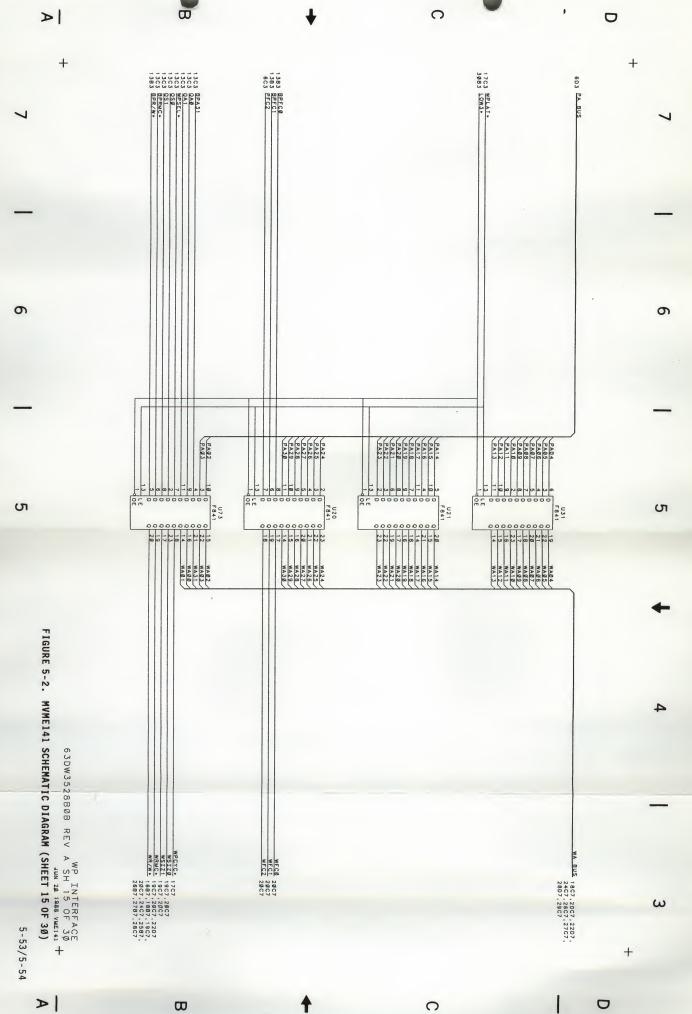

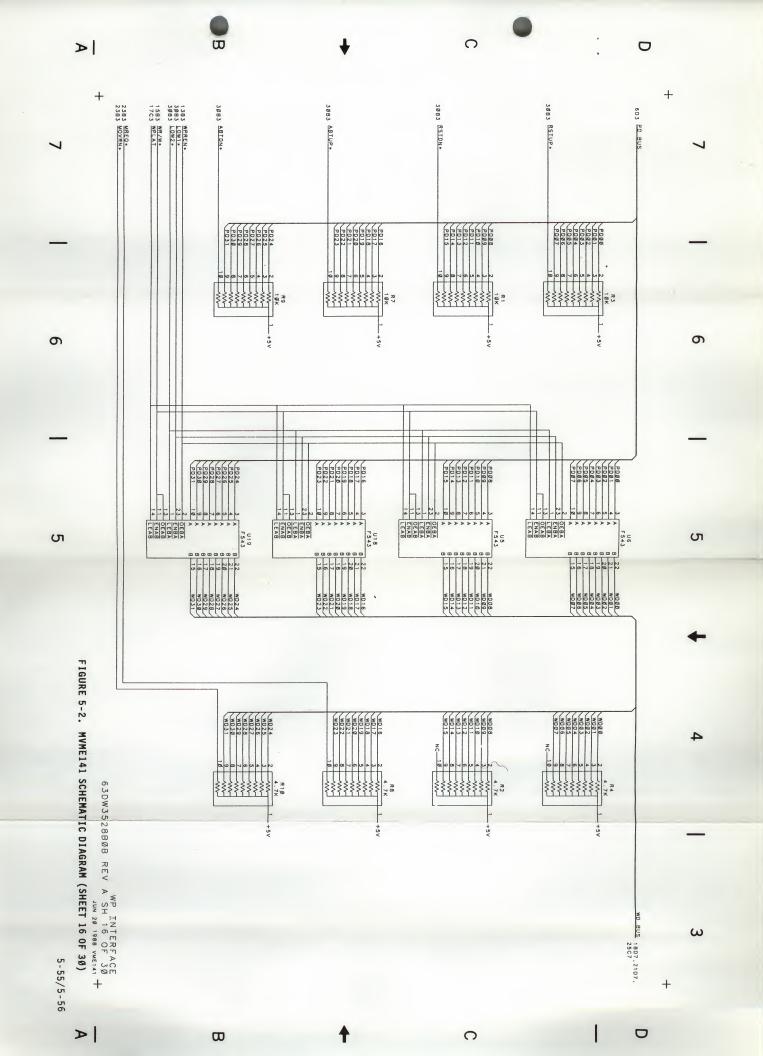

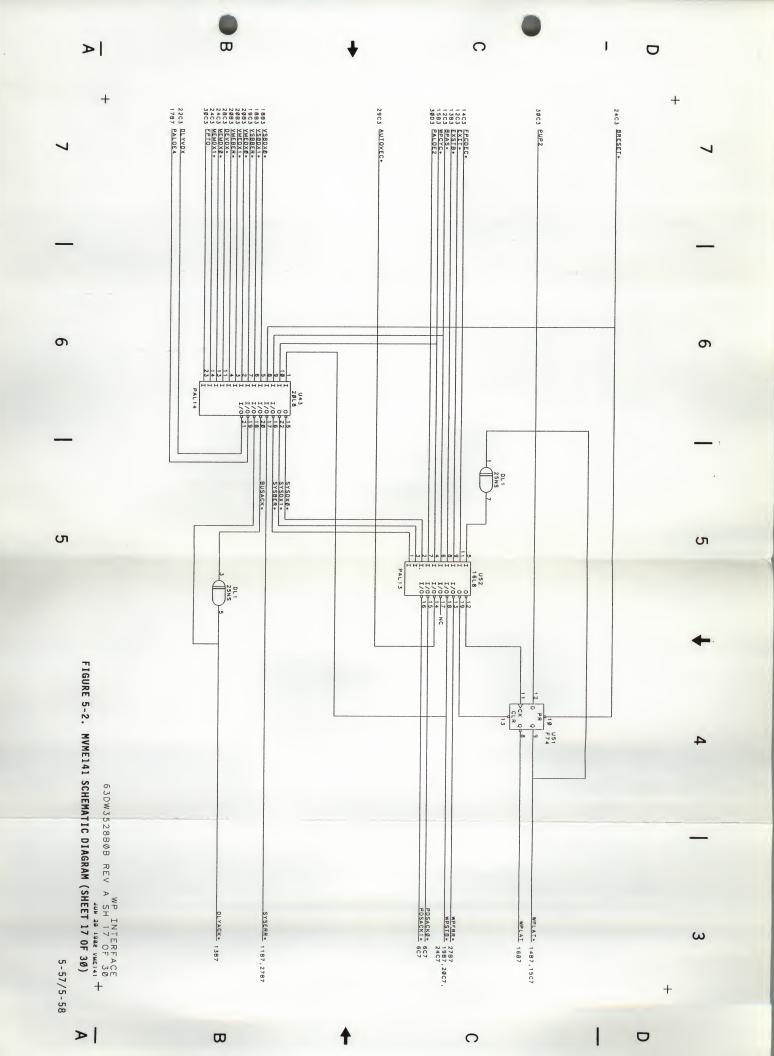

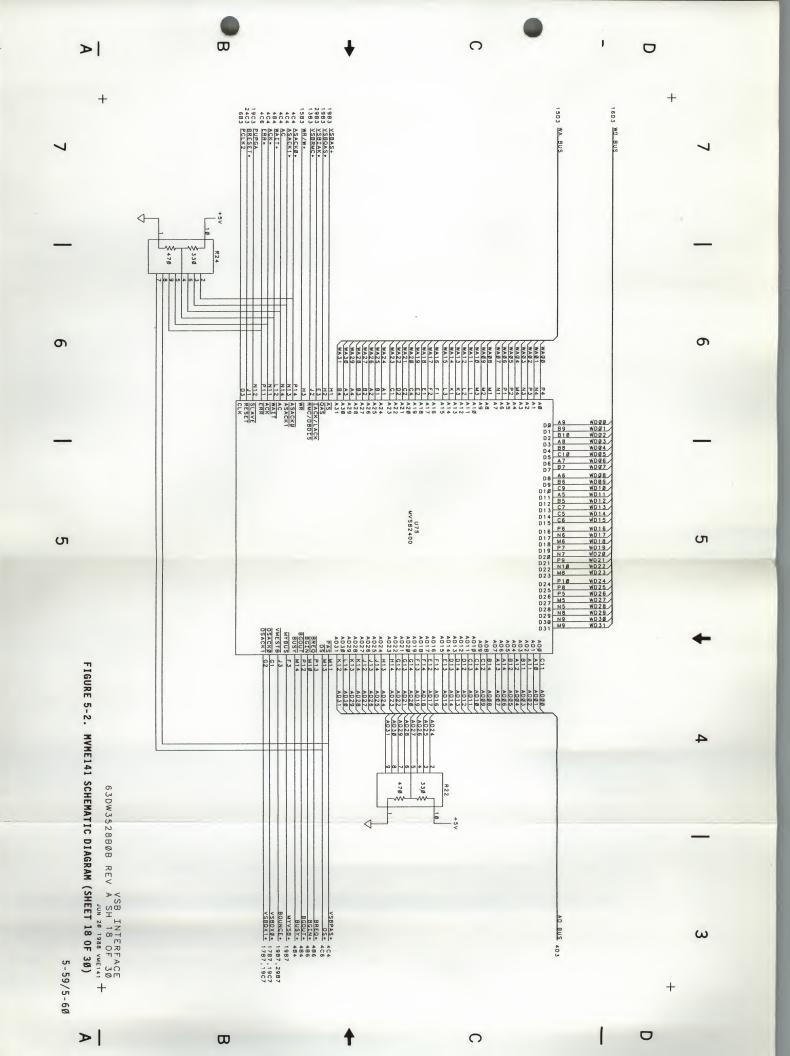

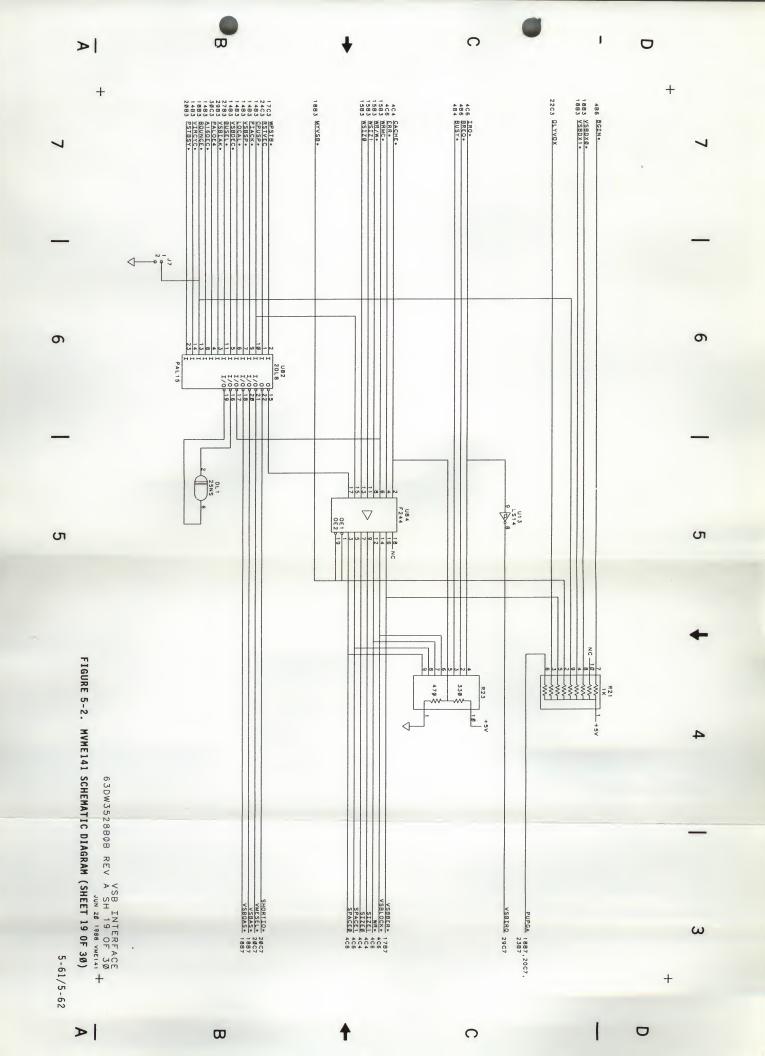

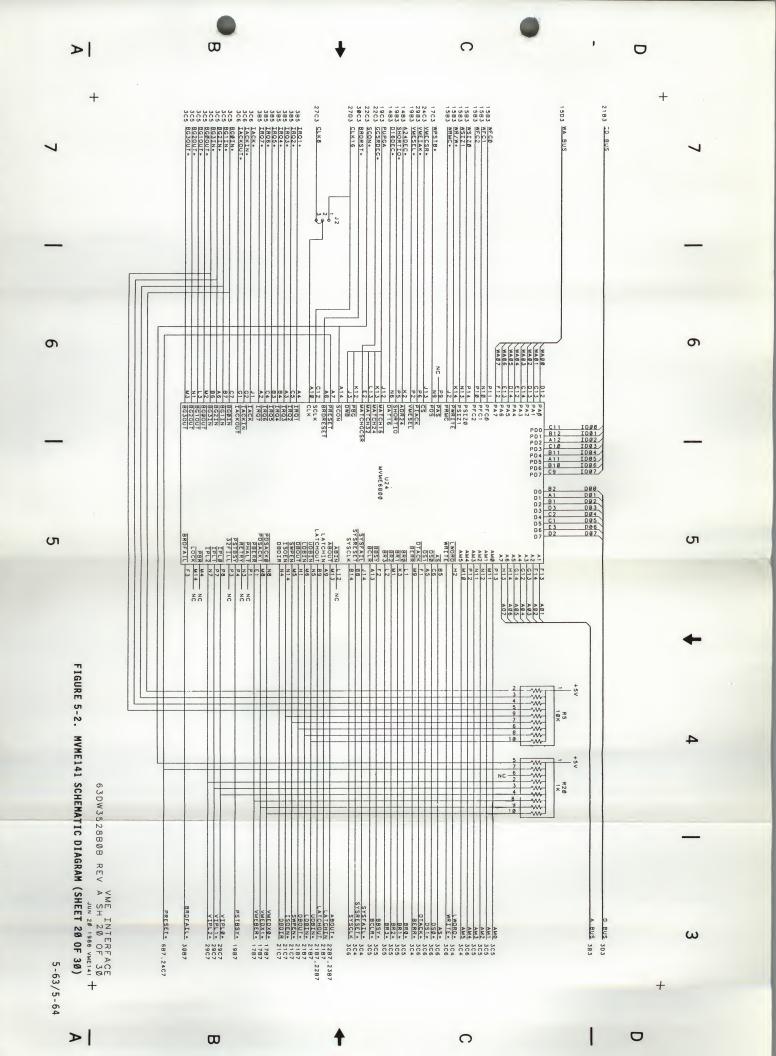

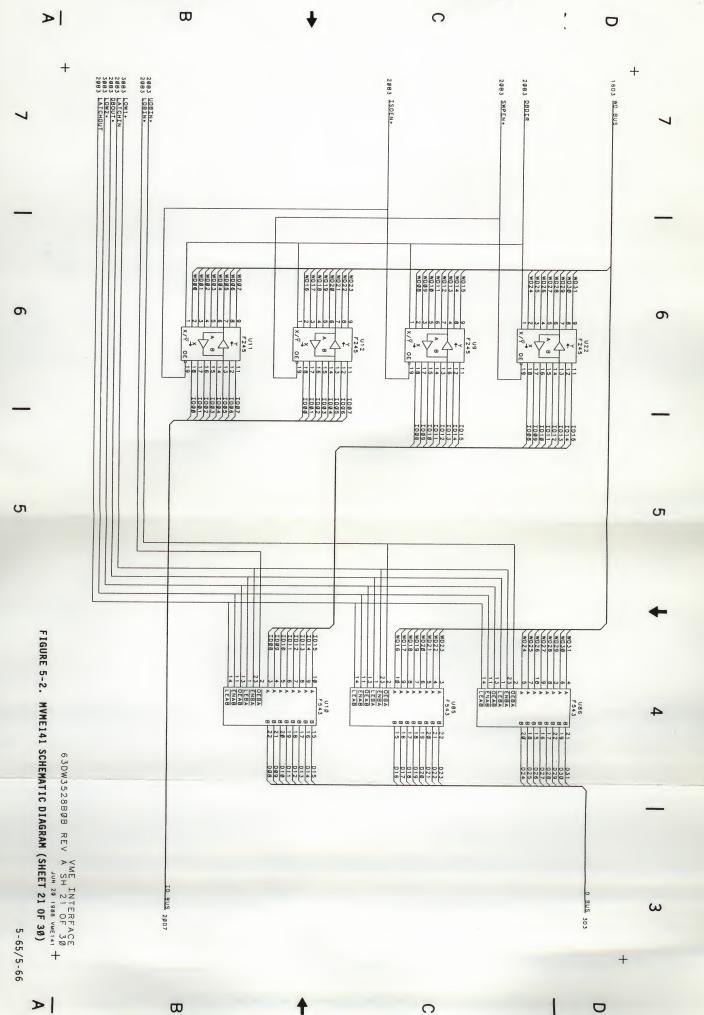

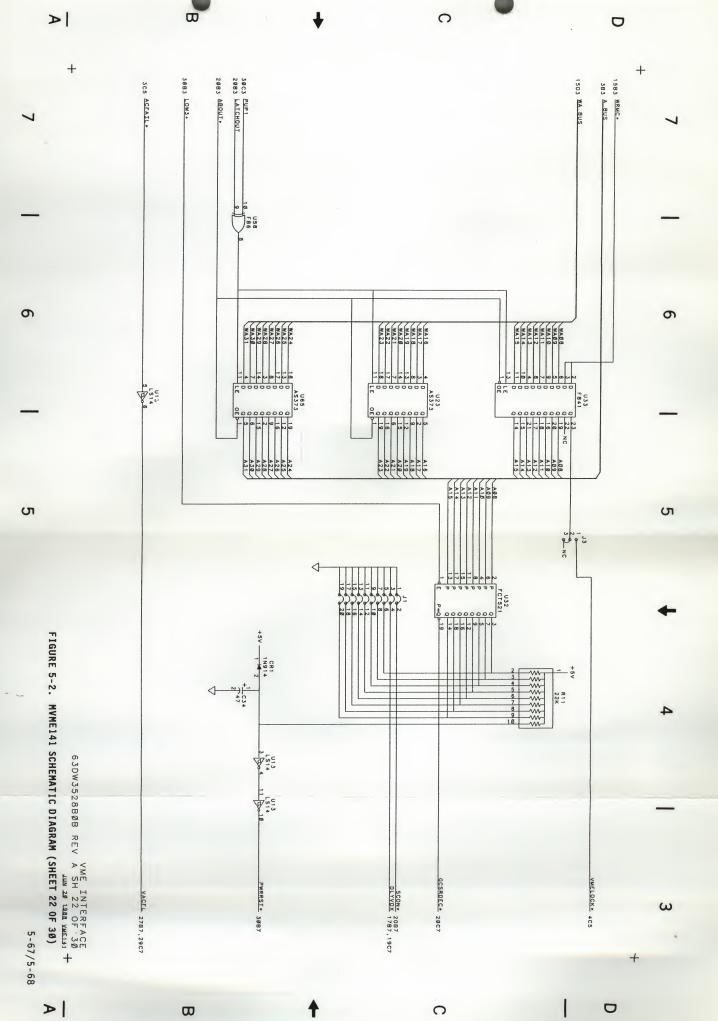

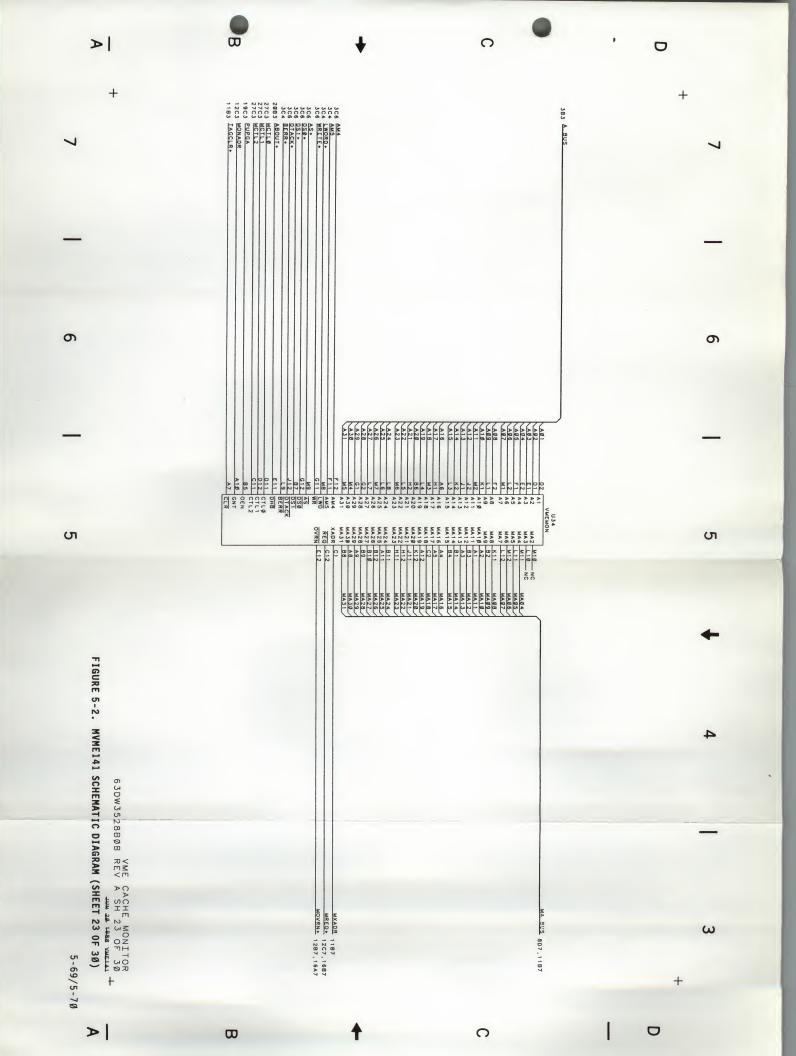

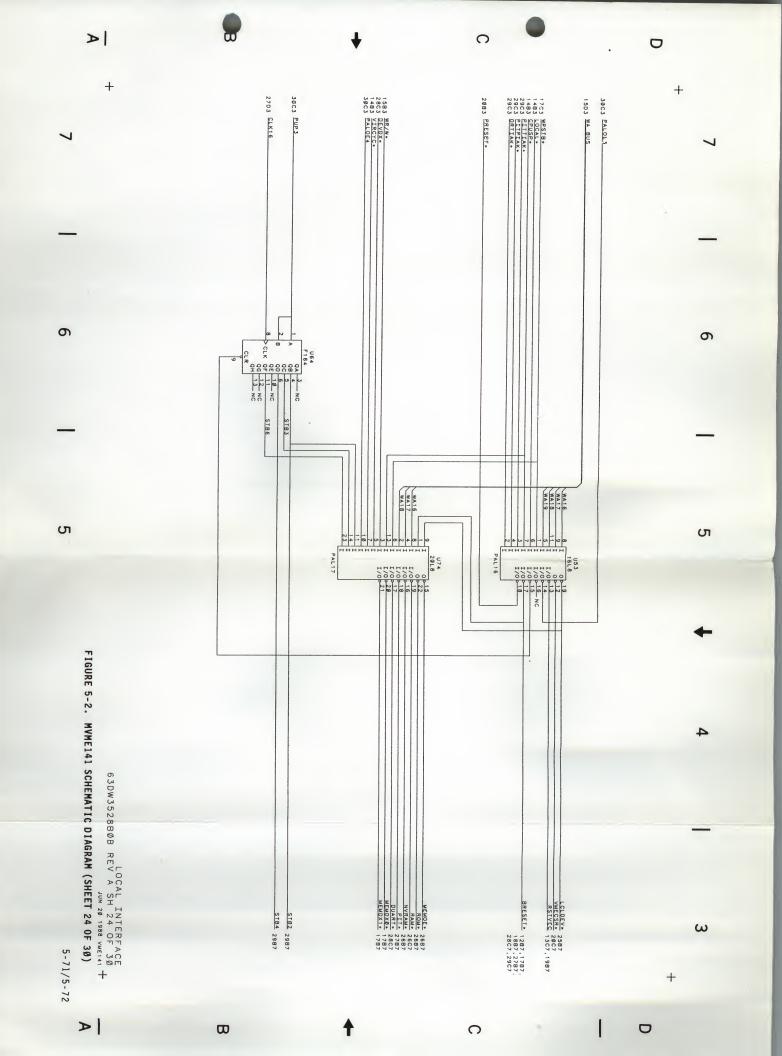

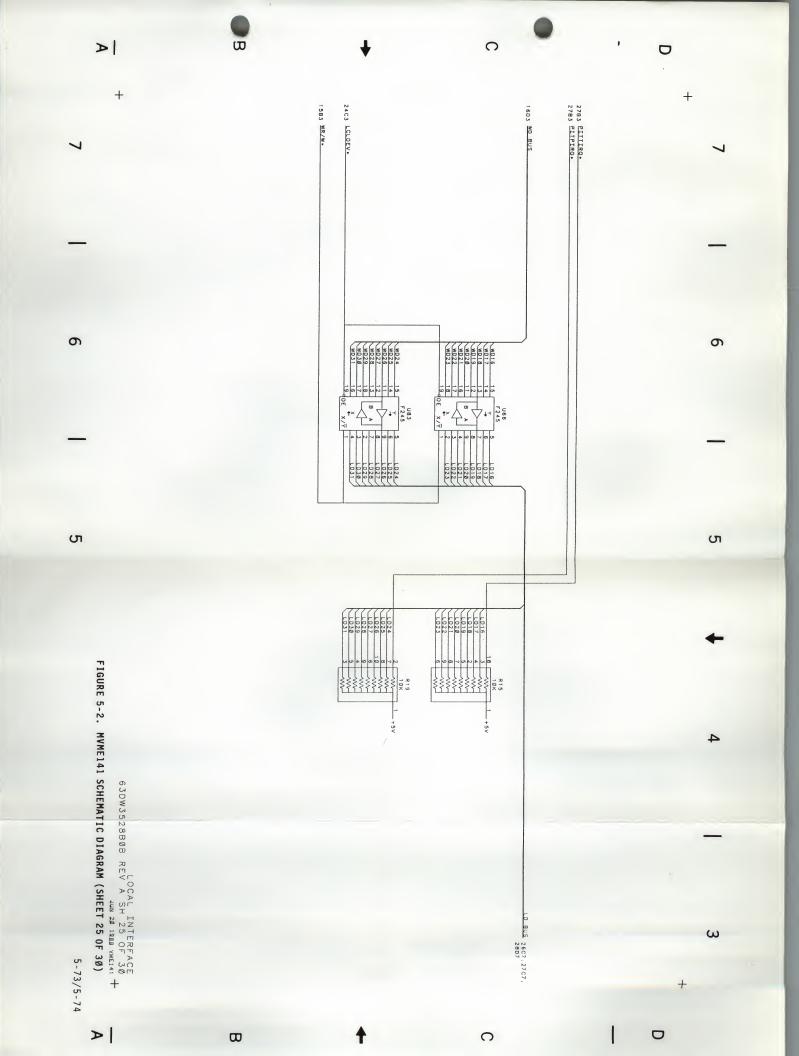

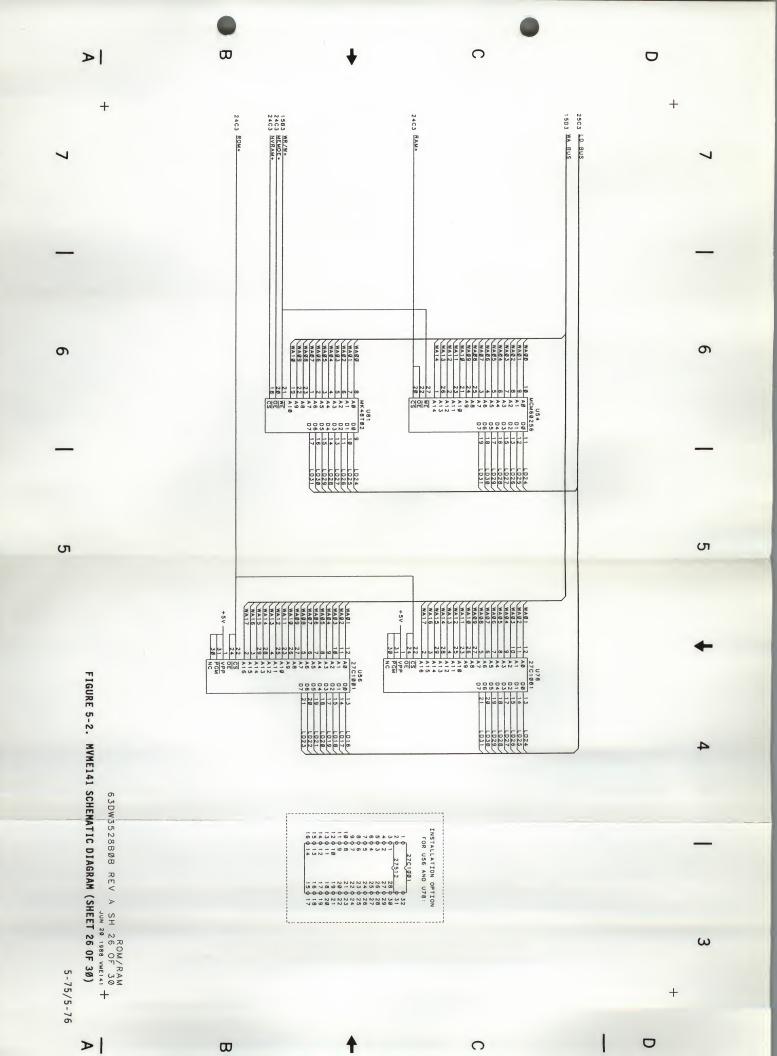

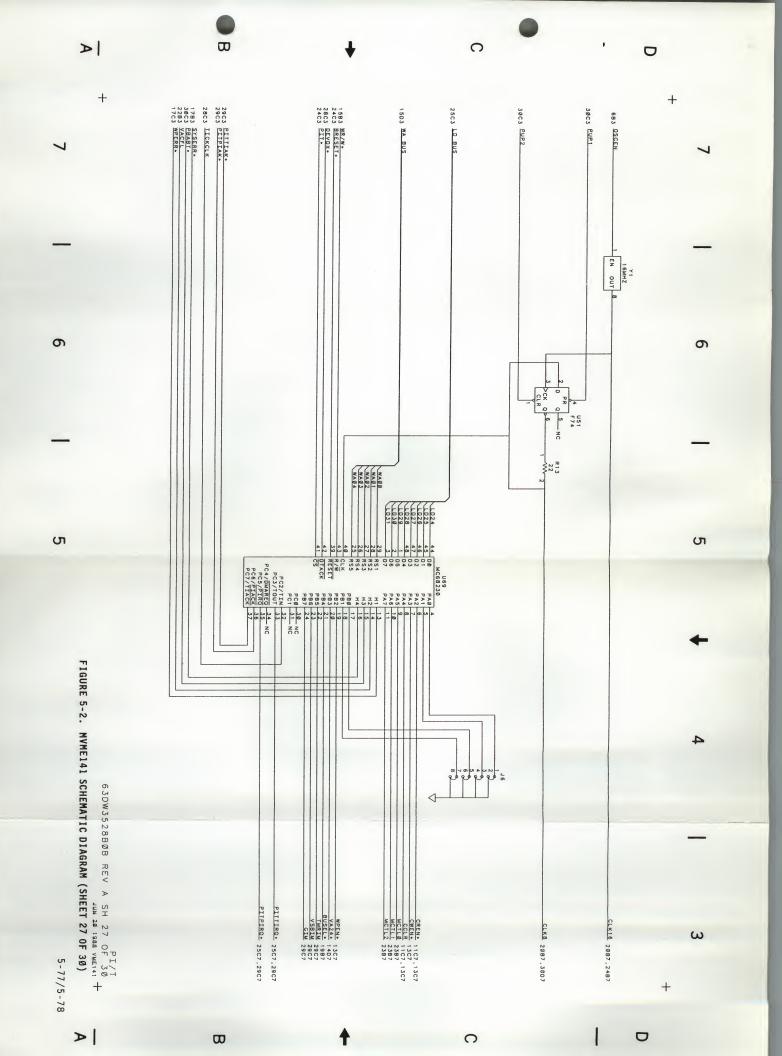

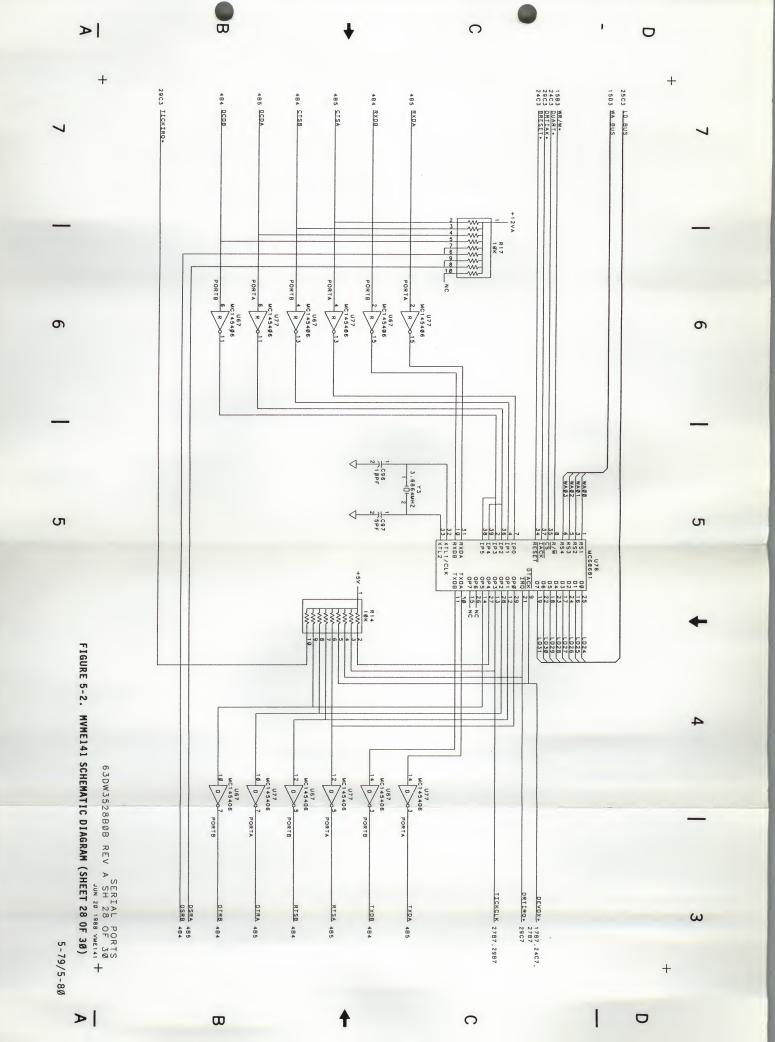

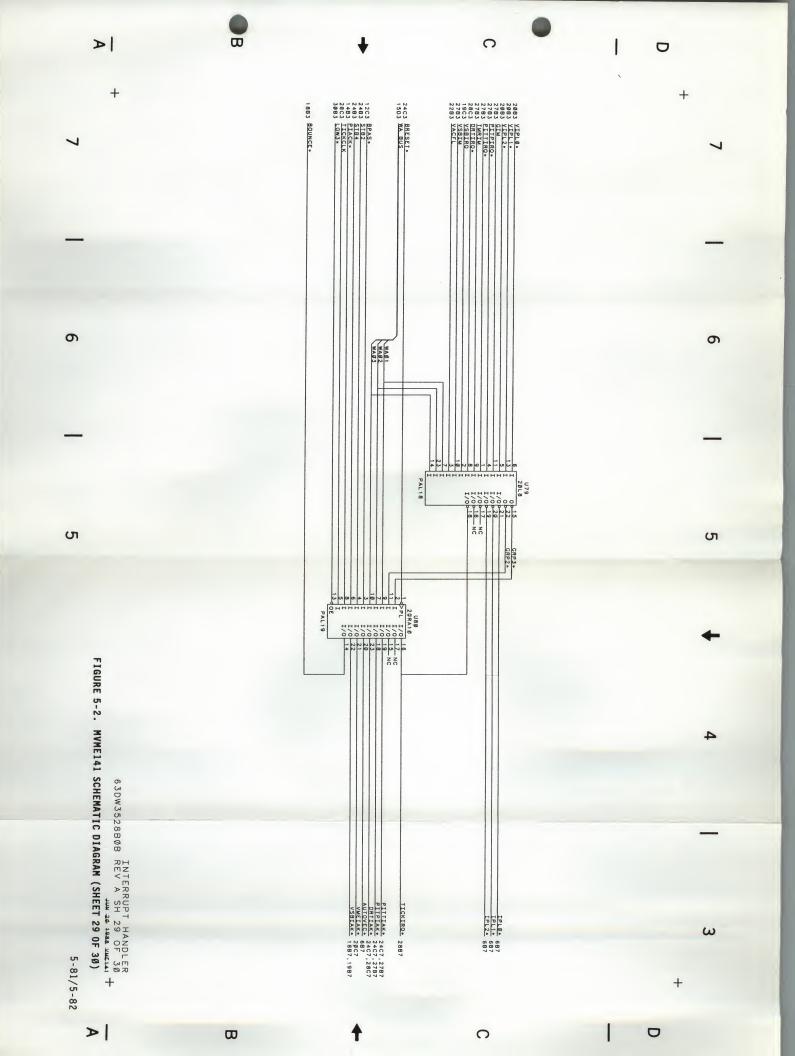

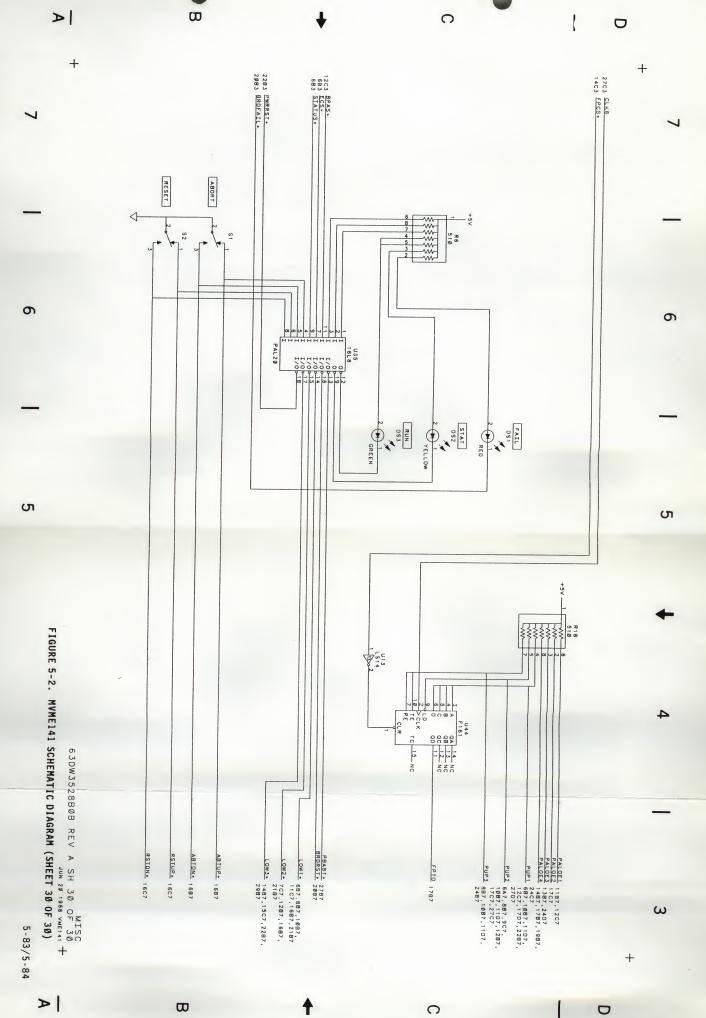

| FIGURE 5-2. | MVME141 SCHEMATIC DIAGRAM                                              |  |

# TABLE OF CONTENTS (cont.)

# LIST OF TABLES

| TABLE 1-1. | MVME141 SPECIFICATIONS 1-2                     |  |

|------------|------------------------------------------------|--|

| TABLE 2-1. | MVME141 JUMPER SUMMARY 2-2                     |  |

| TABLE 2-2. | SERIAL PORT CABLING                            |  |

| TABLE 4-1. | ADDRESS MAP                                    |  |

| TABLE 4-2. | NVRAM/TOD CLOCK REGISTER MAP 4-6               |  |

| TABLE 4-3. | PI/T ADDRESS MAP 4-8                           |  |

| TABLE 4-4. | DUART ADDRESS MAP                              |  |

| TABLE 4-5. | DUART PARALLEL PORT ASSIGNMENTS 4-16           |  |

| TABLE 4-6. | VSBchip REGISTERS 4-17                         |  |

| TABLE 4-7. | VMEchip LOCAL CONTROL AND STATUS<br>REGISTERS  |  |

| TABLE 4-8. | VMEchip GLOBAL CONTROL AND STATUS<br>REGISTERS |  |

| TABLE 4-9. | MVME141 INTERRUPT ASSIGNMENTS 4-22             |  |

| TABLE 5-1. | CONNECTOR P1 PIN ASSIGNMENTS                   |  |

| TABLE 5-2. | CONNECTOR P1 SIGNAL DESCRIPTIONS 5-3           |  |

| TABLE 5-3. | CONNECTOR P2 PIN ASSIGNMENTS                   |  |

| TABLE 5-4. | CONNECTOR P2 SIGNAL DESCRIPTIONS 5-8           |  |

| TABLE 5-5. | CONNECTOR J4 SIGNAL DESCRIPTION 5-12           |  |

| TABLE 5-6. | CONNECTOR J5 SIGNAL DESCRIPTIONS 5-13          |  |

| TABLE 5-7. | MVME141 PARTS LIST 5-14                        |  |

х

### CHAPTER 1 - GENERAL INFORMATION

#### 1.1 INTRODUCTION

This user's manual provides general information, preparation and installation instructions, operating information, and support information for the MVME141 Series of 32-bit VMEbus/VSB-based microcomputers. These modules are referred to as the MVME141 throughout the remainder of this manual.

## **1.2 FEATURES**

The features of the MVME141 microcomputer include:

- MC68Ø3Ø Virtual Memory Microprocessor with 32-bit address and data at 25 or 33.3 MHz.

- MC68882 Floating Point Coprocessor (FPC) at 25 to 33.3 MHz.

- 64Kb of zero wait state physical cache.

- VMEbus Cache Monitor for software transparent cache operation.

- Write-posting interface for fast writes to system memory.

- Two 32-pin, JEDEC standard sockets for ROM/PROM/EPROM.

- $\bullet$  One 24-pin, JEDEC standard socket for a 2K x 8 NVRAM/Time-Of-Day Clock.

- One 28-pin, JEDEC standard socket for 32K x 8 Static RAM.

- Two, front panel, RS-232C serial communications ports (MC68681).

- VSB Master interface using the MVSB24ØØ to provide:

- VSB system controller with bus arbiter.

- VSB requester with programmable timeout module.

- Block transfer module with byte count register.

- Status and Control Register.

- VMEbus Master Interface using the MVME6ØØØ VMEchip to provide:

- VMEbus System Controller with 4-Level Arbiter.

- VMEbus A32/A24/A16, D32/D16/DØ8 Master Interface.

- VMEbus 4-Level Requester.

- VMEbus 7-Level Interrupter.

- VMEbus 7-Level Interrupt Handler.

- Multiprocessor Control and Status Registers.

- VMEbus access, VMEbus cycle, and Local watchdog timers.

- 16-bit programmable timer (MC68681).

- 24-bit programmable counter/timer (MC6823Ø).

- Front Panel RUN, STATUS, and FAIL LED indicators.

- Front Panel RESET and ABORT pushbutton switches.

- Four general purpose, software readable switches.

- VMEbus double-high, single-wide form factor.

## 1.3 SPECIFICATIONS

General specifications for the MVME141 microcomputer are provided in Table 1-1. Sections 1.3.1 and 1.3.2 detail cooling requirements and FCC compliance, respectively.

| Characteristic       | Specification                                                                                                                                                                                                      |  |  |  |  |  |  |

|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Microprocessor       | MC68Ø3Ø 32-Bit Microprocessor                                                                                                                                                                                      |  |  |  |  |  |  |

| Coprocessor          | MC68882 Floating-Point Coprocessor                                                                                                                                                                                 |  |  |  |  |  |  |

| Operating Frequency: |                                                                                                                                                                                                                    |  |  |  |  |  |  |

| MVME141-1            | 25.0 MHZ clock frequency                                                                                                                                                                                           |  |  |  |  |  |  |

| MVME141-2            | 33.3 MHZ clock frequency                                                                                                                                                                                           |  |  |  |  |  |  |

|                      | (The operating frequency for the MC68030 and the MC68882 is set by the oscillator installed at location Y2.)                                                                                                       |  |  |  |  |  |  |

| CACHE                | 64Kb of single-set, direct mapped physical<br>cache supporting two cycle (zero wait state)<br>read accesses at 25 and 33.3 MHz. Write<br>operation is write-through with write-allocate<br>on longword operations. |  |  |  |  |  |  |

| ROM                  | Two 32-pin, JEDEC standard sockets are provided<br>for either 64K x 8 or 128K x 8 size, 25Ø<br>nanosecond or faster EPROMs.                                                                                        |  |  |  |  |  |  |

| SRAM                 | One 24-pin, JEDEC standard socket is provided for a 2K x 8 NVRAM/Time-Of-Day Clock.                                                                                                                                |  |  |  |  |  |  |

|                      | One 28-pin, JEDEC standard socket is provided for a 32K x 8 Static RAM.                                                                                                                                            |  |  |  |  |  |  |

| I/0                  | Two RS-232C asynchronous serial ports are provided using the MC68681 DUART.                                                                                                                                        |  |  |  |  |  |  |

| 1-2                  |                                                                                                                                                                                                                    |  |  |  |  |  |  |

## TABLE 1-1. MVME141 SPECIFICATIONS

| Characteristic                | Specification                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Timers                        | One 24-bit counter/timer is provided through the MC6823Ø PI/T.                                                                                                                                                                                                        |  |  |  |  |  |  |

|                               | One 16-bit tick timer is provided through the<br>MC68681 DUART. (The tick timer interrupt from<br>the DUART is provided as a separate interrupt<br>source from the serial ports.)                                                                                     |  |  |  |  |  |  |

| VSB                           | A VSB system controller and master interface<br>(A32/D32) is implemented using the MVSB24ØØ<br>VSBchip.                                                                                                                                                               |  |  |  |  |  |  |

| VMEbus                        | A VMEbus system controller and master interface<br>(A32/A24/A16, D32/D16/D8) is implemented using<br>the MVME6ØØØ VMEchip. The MVME6ØØØ provides a<br>programmable Arbiter, Requester, Interrupter,<br>Interrupt Handler, Multiprocessor CSR, and<br>watchdog timers. |  |  |  |  |  |  |

| Connectors                    | Both P1 and P2 backplane connectors are used to<br>power the board and to access the VMEbus and VSB.<br>Two 9-pin "D" connectors are provided on the<br>front panel to access the serial ports.                                                                       |  |  |  |  |  |  |

| Power Requirements            | +5Vdc, 5.9 Amps maximum (5.3 A typical)<br>+12Vdc, 25Ø mA maximum<br>-12Vdc, 25Ø mA maximum                                                                                                                                                                           |  |  |  |  |  |  |

| Operating Temperature         | Ø degree to 5Ø degrees C inlet air temperature with forced air cooling.                                                                                                                                                                                               |  |  |  |  |  |  |

| Storage Temperature           | -4Ø degrees to 85 degrees C                                                                                                                                                                                                                                           |  |  |  |  |  |  |

| Relative Humidity             | 5% to 90% (non-condensing)                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Physical Size (PCB):          | VME double-high, single-wide form-factor                                                                                                                                                                                                                              |  |  |  |  |  |  |

| Height x Width<br>Thickness   | 9.2 inches (23.34 cm.) x 6.3 inches (16.00 cm.)<br>0.062 inch (0.157 cm.)                                                                                                                                                                                             |  |  |  |  |  |  |

| Part Projections:             |                                                                                                                                                                                                                                                                       |  |  |  |  |  |  |

| Component Side<br>Solder Side | Ø.5Ø inch (1.27 cm.) maximum<br>Ø.Ø67 inch (Ø.17 cm.) maximum                                                                                                                                                                                                         |  |  |  |  |  |  |

# TABLE 1-1. MVME141 SPECIFICATIONS (cont.)

1-3

### 1.3.1 Cooling Requirements

Motorola VMEmodules are specified, designed, and tested to operate reliably with an incoming air temperature range from  $\emptyset$  degrees C to 55 degrees C (32 degrees F to 131 degrees F) with forced air cooling. Temperature qualification is performed in a standard Motorola VMEsystem 1000 chassis. Twenty-five watt load boards are inserted in the two card slots, one on each side, adjacent to the board under test to simulate a high power density system configuration. An assembly of three axial lead fans, rated at 100 CFM per fan, is placed directly under the MVME card cage. The incoming air temperature is measured between the fan assembly and the card cage where the incoming airstream first encounters the module under test. Test software is executed as the module is subjected to ambient temperature variations. Case temperatures of critical, high power density integrated circuits are monitored to ensure component vendors specifications are not exceeded.

While the exact amount of airflow required for cooling depends on the ambient air temperature and the type, number, and location of boards and other heat sources, adequate cooling can usually be achieved with 10 CFM flowing over the module. Less air flow is required to cool the module in environments having lower maximum ambients. Under more favorable thermal conditions it may be possible to operate the module reliably at higher than 55 degrees C with increased air flow. It is important to note that there are several factors, in addition to the rated CFM of the air mover, which determine the actual volume of air flowing over a module.

#### 1.3.2 FCC Compliance

The MVME141 microcomputer is tested in an FCC-compliant chassis, and meets the requirements for Class A equipment. FCC compliance was achieved under the following conditions:

- 1. Shielded cables on all external I/O ports.

- Cable shields connected to earth ground via metal shell connectors bonded to a conductive module front panel.

- 3. Conductive chassis rails connected to earth ground. This provides the path for connecting shields to earth ground.

- 4. Front panel screws properly tightened.

For minimum RF emissions, it is essential that the conditions above be implemented; failure to do so could compromise the FCC compliance of the equipment containing the modules.

### 1.4 GENERAL DESCRIPTION

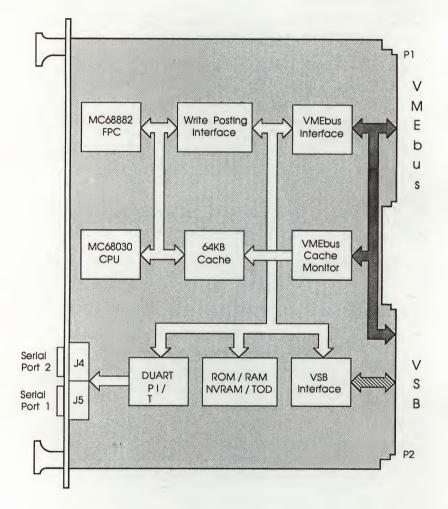

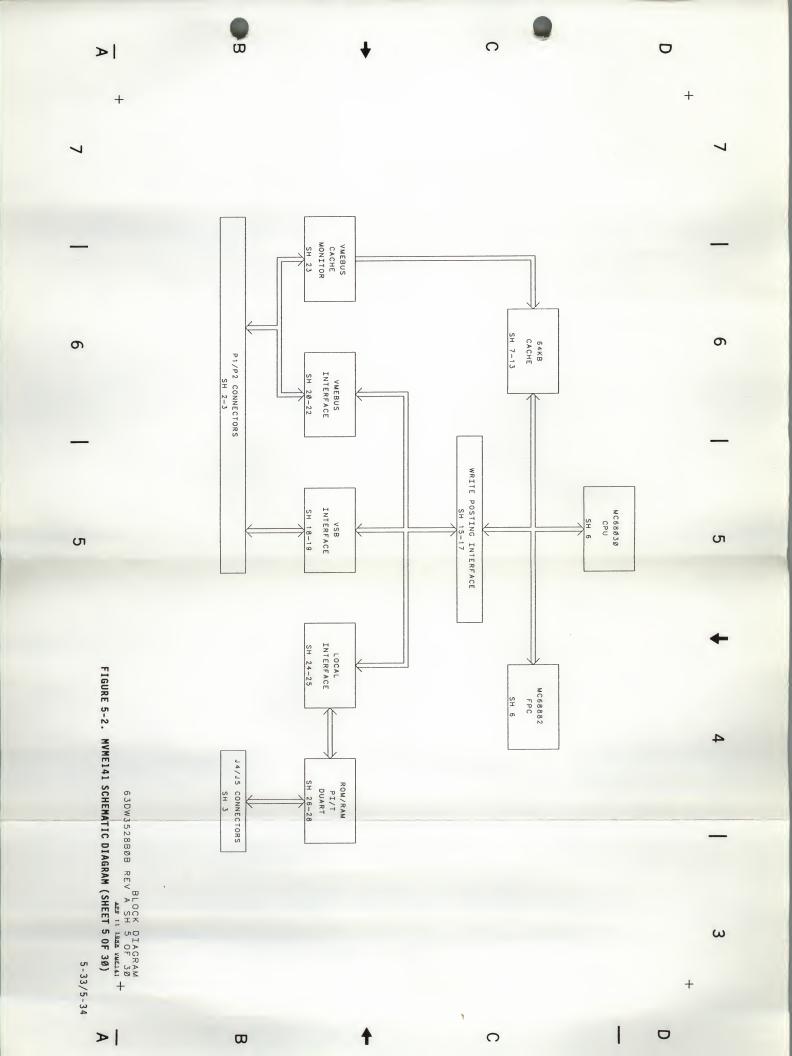

The MVME141 microcomputer is a VMEbus/VSB-based, high-performance, CPU engine utilizing the Motorola MC68030 microprocessor. A block diagram of the MVME141 is illustrated in Figure 1-1.

The MVME141 features 64K bytes of software transparent, zero wait state, physical cache with a write-posting interface. The cache is configured as a single-set, direct-mapped cache containing 4K cache tags with four longword entries (16 bytes) per tag. The cache operates in synchronous mode with the MC68Ø3Ø to provide zero wait state, 2-cycle operation during read hits. During read misses, the cache causes a rerun sequence to the processor while the the writeposting interface simultaneously performs a read access to the target memory. During write operations, the cache operates in a write-allocate, write-through mode in which a cache tag is allocated for longword operations and the target memory is updated along with the cache entry.

Cacheable write operations are latched or "posted" at the writeposting interface. The write-posting interface runs the cycle to the target memory independently so that the processor can continue to operate out of cache while the memory write cycle completes over VSB or VMEbus.

Software transparency for the cache is achieved through a VMEbus Cache Monitor or "Snooper". The Snooper monitors the addresses of all write operations performed on VMEbus by other bus masters in the system. The cache uses the monitored addresses to detect and invalidate any addresses currently valid in the cache memory that have since been modified in system memory.

The MVME141 also features the VME Subsystem Bus (VSB). The VSB provides the processor with a priority port to system memory enabling the MVME141 to continue accessing system memory, even in a heavily active DMA or multiprocessor VMEbus environment. The VSB is implemented with the MVSB24ØØ bus interface chip. The MVSB24ØØ provides a full VSB A32/D32 master interface with system controller support for additional bus masters on VSB.

The MVME141 uses the MVME6000 VMEchip and supporting bus driver chips to implement a VMEbus A32/A24/A16, D32/D16/D8 compatible master interface. The MVME6000 includes the VMEbus system controller functions, a programmable master interface with programmable request level and request/release mode, a 7-level Interrupter and Interrupt Handler, a global register set, four address location monitors, plus other features. The global register set and location monitors provide support for multiprocessing applications. The global register set is accessible as a slave resource by other VMEmodules.

FIGURE 1-1. MVME141 BLOCK DIAGRAM

1-6

The MVME141 includes the MC68882 floating-point coprocessor, the MC68681 DUART for serial I/O and software timing, the MC6823Ø PI/T for local CSR and software counter/timer, two 32-pin JEDEC standard sockets for EPROMs, one 24-pin JEDEC socket for 2K x 8 Non-Volatile RAM/Time-Of-Day Clock, and one 28-pin JEDEC socket for 32K x 8 Static RAM. The static RAM is provided for non-performance critical, private storage of data for applications such as a resident debugger/diagnostic firmware package.

#### **1.5 REFERENCE DOCUMENTATION**

The following publications provide additional helpful information. They describe the VLSI devices, the I/O interfaces, and the firmware used on the MVME141. If not shipped with this product, they may be purchased from the Motorola Literature Distribution Center, 616 West 24th Street, Tempe Arizona 85282; telephone (602) 994-6561.

| DOCUMENT TITLE                          | MOTOROLA<br>PUBLICATION NUMBER |

|-----------------------------------------|--------------------------------|

| MC68Ø3Ø User's Manual                   | MC68Ø3ØUM                      |

| MC68882 User's Manual                   | MC68882UM                      |

| MC68681 DUART                           | ADI-988-R1                     |

| MC6823Ø Parallel Interface/Timer (PI/T) | ADI-86Ø-R2                     |

| VMEbus Specification (Rev C.1)          | HB212/D                        |

| VME Subsystem Bus (VSB) Specification   | MVMESB                         |

| VSBchip User's Manual                   | MVSB24ØØ                       |

| 141BUG User's Manual                    | MVME141BUG                     |

An additional publication that may provide helpful information is the EIA RS-232-C Serial Interface Specification, which is available from the Electronic Industries Association, Washington, D.C.

### 1.6 MANUAL TERMINOLOGY

Throughout this manual, a convention has been maintained whereby data and address parameters are preceded by a character which specifies the numeric format as follows:

| \$ | dollar    | specifies | a | hexadecimal number |

|----|-----------|-----------|---|--------------------|

| %  | percent   | specifies | a | binary number      |

| &  | ampersand | specifies | a | decimal number     |

Unless otherwise specified, all address references are in hexadecimal throughout this manual.

An asterisk (\*) following the signal name for signals which are level significant denotes that the signal is true or valid when the signal is low.

An asterisk (\*) following the signal name for signals which are edge significant denotes that the actions initiated by that signal occur on high to low transition.

In this manual, assertion and negation are used to specify forcing a signal to a particular state. In particular, assertion and assert refer to a signal that is active or true; negation and negate indicate a signal that is inactive or false. These terms are used independently of the voltage level (high or low) that they represent.

## CHAPTER 2 - HARDWARE PREPARATION AND INSTALLATION

## 2.1 INTRODUCTION

This chapter provides the unpacking, hardware preparation, and installation instructions for the MVME141 microcomputer. It also describes the system support requirements and the start-up procedures.

## 2.2 UNPACKING INSTRUCTIONS

## NOTE

If shipping carton is damaged upon receipt, request that the carrier's agent be present during unpacking/inspection of equipment.

Carefully unpack the equipment from the shipping carton. Refer to the packing list and verify that all items are present. Save the shipping carton and packing materials for storing or reshipping of the equipment.

## CAUTION

AVOID TOUCHING AREAS OF INTEGRATED CIRCUITS; STATIC DISCHARGE CAN DAMAGE THESE CIRCUITS.

Inspect for any shipping damage. If no damage exists, then the module can be prepared for operation according to the following sections of this chapter.

## 2.3 HARDWARE PREPARATION

This section describes the hardware preparation of the MVME141 prior to installation. Observance of this description will ensure the user that all components are properly configured for operation.

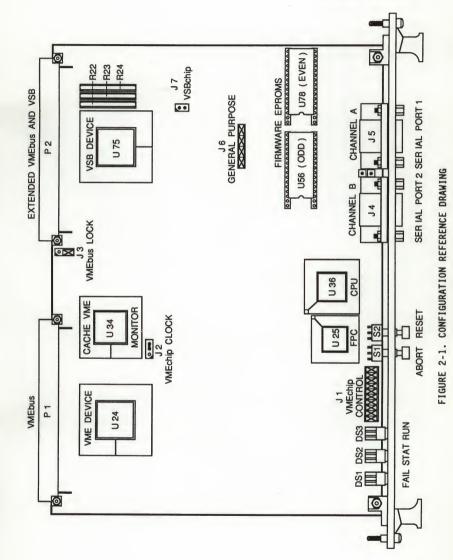

Jumper blocks are used to select various hardware and software functions on the MVME141. They must be properly configured before installation according to the hardware parameters of the board, and according to the user's application of the board in the system. The jumper blocks are illustrated in Figure 2-1 with their factory jumper settings (asterisks indicate the factory settings). The

factory settings configure the board for one common mode of operation. The user should verify and change these jumper settings as required to configure the module for the target application. The jumper functions and settings are summarized in Table 2-1 and described in the following sections.

| Jumper: Function    | Position  | Configuration                                        |

|---------------------|-----------|------------------------------------------------------|

| J1: VMEchip Control | J1(1-2)   | * Installed - System Controller Enabled              |

|                     | J1(3-4)   | * Installed - (Not Used)                             |

|                     | J1(5-6)   | * Installed - Decodes GCSR $A8 = \emptyset$          |

|                     | J1(7-8)   | * Installed - Decodes GCSR A9 = $\emptyset$          |

|                     | J1(9-1Ø)  | * Installed - Decodes GCSR $A1\emptyset = \emptyset$ |

|                     | J1(11-12) | * Installed - Decodes GCSR All = $\emptyset$         |

|                     | J1(13-14) | * Installed - Decodes GCSR A12 = $\emptyset$         |

|                     | J1(15-16) | * Installed - Decodes GCSR A13 = $\emptyset$         |

|                     | J1(17-18) | * Installed - Decodes GCSR A14 = $\emptyset$         |

|                     | J1(19-2Ø) | * Installed - Decodes GCSR A15 = $\emptyset$         |

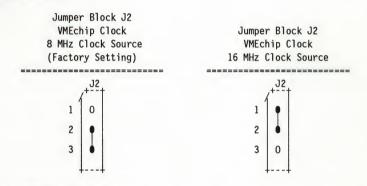

| J2: VMEchip Clock   | J2(1-2)   | Installed - 16 MHz clock source                      |

|                     | J2(2-3)   | * Installed - 8 MHz clock source                     |

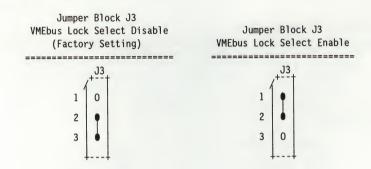

| J3: VMEbus Lock     | J3(1-2)   | Installed - VMEbus Lock Enabled                      |

|                     | J3(2-3)   | * Installed - VMEbus Lock Disabled                   |

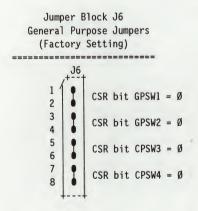

| J6: General Purpose | J6(1-2)   | * Installed - CSR bit GPSW1 = Ø                      |

|                     | J6(3-4)   | * Installed - CSR bit GPSW2 = Ø                      |

|                     | J6(5-6)   | * Installed - CSR bit GPSW3 = Ø                      |

|                     | J6(7-8)   | * Installed - CSR bit GPSW4 = $\emptyset$            |

| J7: VSB chip        | J7(1-2)   | * No Jumper - Normal operation                       |

|                     | J7(1-2)   | Installed - Factory test only                        |

|--|

Notes: Asterisks indicate factory configuration. Designators J4 and J5 are assigned to the DB-9 connectors.

2-3

2

## 2.3.1 VMEchip Control (J1)

Jumper block J1 selects the VMEbus System Controller function and the group address of the global CSR (GCSR) for the VMEchip. Installing a jumper cap at position J1(1-2) will select the MVME141 as the VMEbus system controller. The state of this jumper can be read by the processor through the local CSR (LCSR) in the VMEchip. When selected as system controller, the MVME141 should be installed in the chassis in the left-most card slot relative to the other VMEbus bus masters in the system. Jumper position J1(3-4) is not used. The remaining eight jumper positions on J1 are used to select the group address of the GCSR. The group address of the GCSR is selected for a VMEbus Short I/O access with a match on the eight VMEbus address lines A8 through A15. Each of the jumper positions is assigned to the corresponding VMEbus address line given in Table 2-1 and compared with that address line for a match condition. An installed jumper causes a match for a logic zero on its corresponding VMEbus address line, and a removed jumper causes a match for a logic one. Note that the base address of the GCSR is further decoded within the group by the VMEchip. Refer to the VMEchip User's Manual for a description of the GCSR.

> Jumper Block J1 VMEchip Control (Factory Setting)

|    | ,+-J1 | -  |                                                         |

|----|-------|----|---------------------------------------------------------|

| 1  | 00    | 2  | VMEbus System Controller Enabled.                       |

| 3  | 00    | 4  | Not Used.                                               |

| 5  | 00    | 6  | VMEchip GCSR address, decodes $A8 = \emptyset$          |

| 7  | 00    | 8  | VMEchip GCSR address, decodes A9 = $\emptyset$          |

| 9  | 00    | 1Ø | VMEchip GCSR address, decodes $A1\emptyset = \emptyset$ |

| 11 | 00    | 12 | VMEchip GCSR address, decodes All = $\emptyset$         |

| 13 | 00    | 14 | VMEchip GCSR address, decodes A12 = $\emptyset$         |

| 15 | 00    | 16 | VMEchip GCSR address, decodes A13 = $\emptyset$         |

| 17 | 00    | 18 | VMEchip GCSR address, decodes A14 = $\emptyset$         |

| 19 | 00    | 2Ø | VMEchip GCSR address, decodes A15 = $\emptyset$         |

| -  |       |    |                                                         |

2

## 2.3.2 VMEchip Clock Select (J2)

Jumper block J2 selects the clock source for the VMEchip. A jumper at setting J2(2-3) will select 8 MHz operation. This jumper is implemented as a soldered-in staple, and it is not recommended for modification by the user. Note that at initial release, the VMEchip is not specified for operation at 16 MHz on the MVME141. If 16 MHz operation (setting J2(1-2)) is selected and in question, contact a factory representative for verification of the jumper configuration.

## 2.3.3 VMEbus Lock Select (J3)

Jumper block J3 selects the resource lock control for VMEbus RMC (Read Modify Cycle) operations. The resource lock on VMEbus is a unique feature supported on certain Motorola VMEmodules that contain dual-port memory resources. It is used to support the CAS and CAS2 instructions of the MC68020 and MC68030 microprocessors. For these instructions, multiple memory cycles to different addresses may be executed during a single indivisible RMC operation. The resource lock control is provided to ensure the indivisibility The resource lock control is provided to ensure the indivisionity of these cycles to the dual-port boards. The resource lock is implemented by driving the RMC\* signal from the processor onto the VMEbus reserved pin P2-B3 during VMEbus operations. The supporting dual-port boards use this signal when asserted as a port lock control to prevent the alternate memory port from gaining access to the memory resource during the indivisible block of cycles. Jumper J3 should only be set to the lock-enabled position (setting J3(1-2)) if a dual-port memory resource on VMEbus supports the resource lock control, and if the VMEbus reserved pin is not otherwise used in the system. With jumper block J3 set to the lock-disabled position (setting J3(2-3)), no connection is made to the VMEbus reserved pin. Jumper block J3 is factory configured for the lock-disabled function.

#### 2.3.4 General Purpose Jumpers (J6)

Jumper block J6 provides four general purpose jumpers that are readable by software and perform no hardware functions directly. They can be used as software switches by the software or firmware running on the board to select various program-controlled functions. The jumper positions are readable through the GPSW1 through GPSW4 bits of the PI/T CSR. An installed jumper reads as a logic zero from its corresponding CSR bit, and a removed jumper reads as a logic one. The PI/T CSR bits are described in section 4.2.5.1. If the 141Bug firmware EPROMs are installed, refer to the 141Bug User's Manual for the functional assignments for these jumpers.

### 2.3.5 VSBchip Jumper (J7)

Jumper block J7 is provided for factory test purposes only. No jumper cap should be installed at this location.

Jumper Block J2 VSBchip Jumper No Jumper Installed (Factory Setting)

#### 2.3.6 Firmware EPROMs

Two firmware EPROMs are required on the MVME141 to provide the start-up program for the MC68Ø3Ø after a power-up or reset condition. The EPROMs should be installed at chip locations U56 and U78 on the MVME141. These chip locations are implemented as two 32-pin, raised DIP sockets that can accept either two JEDEC compatible, 28-pin, 64K x 8 EPROMs, or two JEDEC compatible, 32-pin, 128K x 8 EPROMs. Both EPROMs should be of the same type, and either type can be used without any jumper modifications. If 28-pin sockets (closer to the board edge) as illustrated in Figure 2-1. EPROMs with a speed of 25Ø nanoseconds or faster can be used.

The 141Bug firmware product from Motorola is optionally supplied for the MVME141. When installed on the board, the 141Bug uses the general purpose jumpers at jumper location J6 for system configuration. These jumpers must be properly configured before installation. Generally, these jumpers are used as software switches to enable or disable the major features of the MVME141, and they should normally be installed to select the preferred enabled states. For a further description of the configuration controls and operating instructions for the 141Bug firmware, refer to the 141Bug User's Manual.

#### 2.3.7 VSB Bus Termination

Resistor terminations are used on the VSB bus to optimize the electrical characteristics of the VSB signal lines. They may be located either on the processor board or on the VSB backplane. The MVME141 provides three 330/470 ohm, 10-pin SIP resistor networks at

component locations R22, R23, and R24 (by the P2 connector) for the VSB signal terminations. These resistor networks may require removal from the board depending upon the type of VSB backplane used and the number of MVME141s installed on the same VSB bus. The resister networks are socketed on the MVME141 for easy removal.

The resister networks should be configured on the MVME141 so that there is only one set of terminators on the VSB bus, and so that the terminators are located at the left or rightmost card slot of the bus. If a VSB backplane with integral termination resistors is used, then the three resistor networks on the MVME141 should be unplugged from the board. If a VSB backplane without termination resistors is used (such as a ribbon cable and connector backplane), then the three resistor networks on the MVME141 should remain installed on the board if it is the only VSB master or if it is the correct left or rightmost board.

#### 2.4 SYSTEM SUPPORT

The MVME141 is designed to operate in a VMEmodule system. To support the module in the system, the VMEbus P2 connector should be fully supported for power, for the extended VMEbus, and for the VSB bus. For optimum performance, the VSB memory modules in the system should be jumpered for "cycle start" on address strobe if supportable. In addition, the RS-232 cables must be supplied for the front panel serial ports. Compatible chassis, VME/VSB memory modules, and serial port distribution boards that support the MVME141 are available from Motorola.

#### 2.4.1 Power Distribution

The MVME141 draws electrical power from both the P1 and the P2 connectors. Both connectors must be fully supported for +5 Volt power distribution. If the power connections for the P2 connector are not supported on the backplane, then the MVME141 will be unable to draw enough power from the P1 connector only to operate reliably, and the excessive power draw through P1 only may damage the P1 connector on the board or on the backplane. For optimum reliability, the power distribution for the P1 and P2 connectors should be integrated into a single, monolithic, multilayer backplane utilizing individual power and ground planes.

#### 2.4.2 Extended VMEbus

The MVME141 uses the P2 connector to connect to the extended address and data sections of VMEbus. The extended address bus contains the VMEbus address lines A24 through A31, and provides for system expandability. The extended data bus contains the VMEbus data lines D16 through D31, and provides for increased data throughput and system performance. The extended buses may or may not be supported

2-8

in the system depending on the backplane configuration and the VMEmodules installed. The use of the extended buses by the MVME141 may be enabled or disabled through the CSR bits in the MVME6000 VMEchip, through the VA24 bit in the PI/T CSR, and through certain predefined ranges of the MVME141 address map. The extended data bus, however, must be supported in the system to any memory module residing in the MVME141 cacheable address space. The MVME141 only supports caching to 32-bit wide data ports, and it performs all read accesses to its cacheable address space as 4-byte, longword-aligned data transfers. If a D16 module is located in the cacheable address space, the MVME141 will not be able to access the odd-word addresses on the module. Refer to section 4.5.1 on the definition of cacheablity. The extended address and data sections of the VMEbus occupy the center row of the P2 connector. They should be integrated into the PCB backplane of the chassis for optimum electrical characteristics. Refer to the VMEbus Specification for a description of the VMEbus signals and backplane requirements.

#### 2.4.3 VSB Cabling

The MVME141 uses the P2 connector to connect to the VSB bus. The VSB (VME Subsystem Bus) is an independent data transfer bus that provides an alternate port to system memory for increased performance in a DMA or multiprocessor VMEbus system. The VSB bus may or may not be supported in the system depending on the backplane interconnection and the memory modules installed. The use of the VSB bus by the MVME141 may be enabled or disabled through the CSR bits in the MVSB240 $\emptyset$  VSB chip. The VSB bus occupies the two outer rows of the P2 connector. These outer rows are provided in the VMEbus specification for user applications, and they are normally unconnected on the VMEbus backplane. These outer rows must be bussed on the backplane from the MVME141 card slot to the card slots of the memory modules or other modules in the chassis that support the VSB bus.

The VSB bus interconnection is typically implemented with a ribbon cable and connectors (or a monolithic PCB with connectors) that presses onto the P2 connector pins which extend out from the back of the VMEmodule backplane. A ribbon cable backplane will not support the proper bus grant daisy-chain for VSB. It will be suitable, however, for one to two VSB bus masters as long as the bus grant in and bus grant out lines are shorted together by at least one module on the bus. The memory module will typically serve this function. If three or more VSB masters are required on the same bus, then a PCB VSB backplane must be used that implements the bus grant daisy-chain properly. The VSB bus physical length is limited to 6 card slots. Refer to the VSB Specification for a description of the VSB bus signals and backplane requirements. Refer also to section 2.3.7 for the VSB bus termination requirements. 2

## 2.4.4 VSB Cycle Start

Some VSB memory modules provide a jumper to select the start-ofcycle condition either on the assertion of the VSB address strobe, or on the assertion of the VSB data strobe. The jumper selection depends on whether the VSB master performs address-only cycles in which a VSB resource is selected by an address but no data transfer is performed to it. Note that "bounce" cycles on VSB are addressonly cycles, but that they do not select a target resource on VSB so they do not fall into this category of cycles. The MVME141 does not perform address-only cycles to target resources, so the VSB slave modules can be configured for start-of-cycle on VSB address strobe provided that other VSB masters on the bus, if any, do the same. Generally, start-of-cycle on address strobe for the slave modules will allow for higher performance operation with the MVME141. Refer to the user's manuals of the VSB memory modules in the system for their start-of-cycle jumper configurations.

#### 2.4.5 RS-232 Cables

The RS-232 cables must be supplied to connect to the two front panel serial ports. Each serial port uses a 9-pin, female "D" connector with the pin assignments listed in the leftmost column of Table 2-2. Each port provides the standard RS-232C handshake signals RTS, CTS, DTR, DCD, and DSR. The input handshake signals CTS and DCD are pulled-up at each connector to support basic 3-wire operation using only TXD, RXD, and GND. Refer to section 4.2.6.1 for a description of the handshake signals.

| MVME141 Connector<br>DB-9 | SIGNAL I/O |              | DTE/TERM<br>B-25) |              |        | DCE/MODEM<br>B-25) |

|---------------------------|------------|--------------|-------------------|--------------|--------|--------------------|

| TXD, 3<br>RXD, 2          | ><br><     | RXD,<br>TXD, |                   | TXD,<br>RXD, |        |                    |

| RTS, 7<br>CTS, 8          | ><br><     | CTS,<br>RTS, |                   | RTS,<br>CTS, | 7<br>8 | (4)<br>(5)         |

| DTR, 4<br>DCD, 1          | ><br><     | DCD,<br>DTR, |                   | DTR,<br>DCD, |        |                    |

| DSR, 6<br>GND, 5          |            | DSR,<br>GND, | (6)<br>(7)        | DSR,<br>GND, |        |                    |

| TΔ  | BL | F        | 2 - | 2  | S | ER  | T A |   | Pn | P          | Т | C | A R | 1   | TN | IG. |  |

|-----|----|----------|-----|----|---|-----|-----|---|----|------------|---|---|-----|-----|----|-----|--|

| 1 1 | DL | <b>E</b> | - ۲ | ۷. | 3 | C R | 1 P | 1 | ΓU | <b>' N</b> |   | 6 | 40  | - L | 11 | 10  |  |

Notes: Signal names on the left are at the MVME141 connector. Signal names on the right are on the cable. DSR on the MVME141 is a pull-up resistor to +12V. DB-9, pin 9 (DB-25, pin 1) is not connected.

Both serial ports on the MVME141 are configured at the DUART controller chip as DTEs (Data Terminal Equipment), so null-modem cables will generally be required to connect to other terminal equipment. The recommended cabling configurations are given in Table 2-2 for connecting to other computer equipment using either DB-9 or DB-25 connectors. Note that the connector pinouts or the use of the handshake signals may vary with other computer equipment, so other cabling configurations may be required than those given in the table. The use of shielded cables is recommended to reduce the generation and susceptibility of EMI (Electro Magnetic Interference).

## 2.4.6 Serial Distribution Boards

Serial distribution boards are available from Motorola for the front panel serial ports on the MVME141. The MVME714 from Motorola can be used to translate the front panel DB-9 connectors to DB-25 connectors, to allow the serial ports to be individually reconfigured from DTEs (Data Terminal Equipment) to DCEs (Data Computer Equipment), and to enable the routing of the serial port cables to the rear of the chassis. The MVME714M from Motorola is a similar product that includes a modem interface for a direct telephone hook-up. Note that the use of a serial transition board may alter the cabling requirements described in section 2.6.5.

## 2.5 INSTALLATION INSTRUCTIONS

After the MVME141 has been properly configured for operation, it is ready for installation in a VMEmodule chassis.

#### CAUTION

INSERTING OR REMOVING THE MODULE WHILE POWER IS APPLIED CAN DAMAGE THE MODULE CIRCUITRY. AVOID TOUCHING AREAS OF INTEGRATED CIRCUITS; STATIC DISCHARGE CAN DAMAGE THESE CIRCUITS.

Ensure that power is turned off to the chassis, and that the card ejector handles are in their non-eject positions. Slide the board into the board slides of the selected slot until the P1/P2 connectors align and seat into their backplane sockets. Press firmly on the top and bottom sections of the front panel until the connectors seat fully into their backplane sockets. Avoid pressing against the card ejector handles as they may slide into their card eject positions. Also avoid pressing against the pushbutton switches or other projections from the front panel as they can be physically damaged. When installing, check the position of the two 2

captive screws at the top and bottom ends of the front panel. They may jam against the chassis frame and prevent the board from seating fully.

Once installed, screw in the two captive screws to secure the board in place. Avoid over-tightening the screws as they may strip out the screw sockets. The screws also serve to electrically connect the front panel to the frame of the chassis by pressing the conductive top and bottom sections of the front panel against the conductive frame of the chassis. This integrates the front panel into the EMI (Electro Magnetic Interference) shield of the chassis. This also completes the termination for the cable shield if shielded serial port cables are used, and it reduces the susceptibility of the board to static discharge that can result from touching the front panel. These EMI protections rely on the use of a chassis that is properly designed to control the susceptibility and emission of EMI.

#### 2.6 START-UP

After the MVME141 has been properly configured and installed in a VMEmodule chassis, it is ready for power-up. Connect a console terminal to serial port 1 of the MVME141, and turn power on to the chassis. The front panel FAIL and STAT LEDs should illuminate during the power-up reset period (or after any reset condition). The power-up reset period should typically last less than a second. After the reset period is complete, the FAIL LED should remain illuminate to indicate that the board is in a start-up "non-ready" mode of operation, the STAT LED should go dim or out, and the RUN LED should illuminate to indicate that the processor is operating. The RUN and STAT LEDs together give a rough indication of how the processor is operating. Refer to section 3.2 for a description of the LED indicators.

After any power-up or reset condition, the processor will begin executing the firmware supplied in the EPROMs. If the 141Bug firmware EPROMs are installed, the processor will perform a selftest and initialization sequence. Upon successful completion, it will turn the FAIL LED off, search for system memory and controller boards installed (if directed by its configuration parameters), output a start-up message to the console screen, and wait for user input (or begin booting if directed).

### **CHAPTER 3 - OPERATING INSTRUCTIONS**

#### 3.1 INTRODUCTION

This chapter describes the operating controls and indicators on the MVME141 microcomputer.

#### 3.2 LED INDICATORS

The MVME141 has three LED indicators (FAIL, STAT, and RUN) located on the front panel. These indicators help to indicate the operation of the processor.

#### 3.2.1 FAIL Indicator (DS1)

The FAIL LED indicator illuminates red while the BRDFAIL (Board Fail) bit of the System Controller Configuration Register in the LCSR of the VMEchip is asserted. It indicates that the MVME141 is driving the SYSFAIL signal on the VMEbus (provided the ISF bit in the GCSR of the VMEchip is not asserted). Refer to the VMEchip User's Manual for a description of the LCSR and GCSR control bits.

The BRDFAIL bit of the VMEchip is asserted after any power-up or reset condition. Generally, the processor should turn off the BRDFAIL bit (thereby turning off the FAIL LED and releasing the SYSFAIL signal on the VMEbus) to indicate that it has successfully passed a self-test procedure and is ready for normal operation. The processor should re-assert the BRDFAIL bit (thereby illuminating the FAIL LED and asserting the SYSFAIL signal on VMEbus) whenever a significant error has occurred as defined by the user's application of the board.

#### 3.2.2 STAT Indicator (DS2)

The **STAT** LED indicator illuminates yellow while the STATUS signal from the processor is asserted. The STATUS signal indicates several states of the processor. It asserts statically to indicate that the processor is halted or reset. It also asserts dynamically (pulses) while the processor is operating to indicate various states of the operation of the internal execution unit of the processor. As such, the **STATUS** LED will illuminate brightly while the processor is reset or halted, and it will also illuminate dimly or brightly while the processor is operating normally. In general, the following operations can be roughly interpreted from the **RUN** and **STATUS** LEDs.

## OPERATING INSTRUCTIONS

| RUN LED | STATUS LED | Indication                    |

|---------|------------|-------------------------------|

| Off     | Off        | Stopped (no program activity) |

| Off     | On         | Halted or Reset               |

| On      | Off        | Bus Locked                    |

| On      | Dim/Bright | Normal Operation              |

## 3.2.3 RUN Indicator (DS3)

The **RUN** LED illuminates green while the AS\* (address strobe) or the ECS\* (Early Cycle Start) signal from the processor is asserted. It indicates that the processor is performing accesses to off-chip resources or to its on-chip cache.

### **3.3 PUSHBUTTON CONTROLS**

The MVME141 has two pushbutton-type switches (**RESET** and **ABORT**) located on the front panel. These switches can be used to restart or abort the operation of the processor.

#### 3.3.1 ABORT Switch (S1)

The **ABORT** switch, when pressed, generates a falling-edge signal transition on the H2S pin of the PI/T chip. The PI/T should be properly configured to generate a level 7 interrupt to the processor on this signal transition.

#### 3.3.2 RESET Switch (S2)

The **RESET** switch, when pressed, asserts the BRDRESET (Board Reset) signal to the VMEchip. The VMEchip then resets all devices on the MVME141, and if jumpered as a system controller, it asserts the SYSRESET signal on VMEbus to reset all the boards in the system. The VMEchip is also reset by this switch. The **RESET** switch is debounced but not timed on the MVME141. It should be held pressed momentarily before releasing. The resulting reset generated by the VMEchip is timed for a minimum assertion of 200 milliseconds.

## CHAPTER 4 - FUNCTIONAL DESCRIPTION

### 4.1 INTRODUCTION

This chapter provides the operating and programming information for the MVME141 microcomputer.

### 4.2 ADDRESS MAP

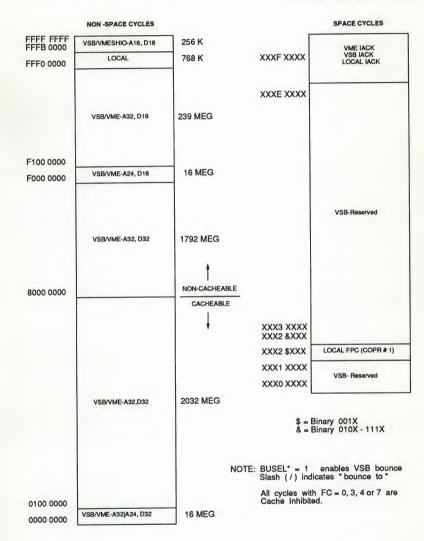

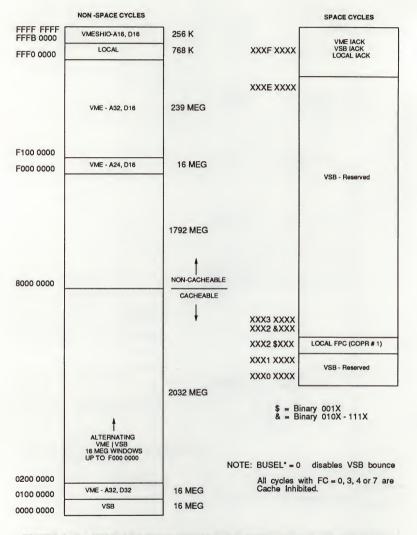

The address map for the MVME141 is given in Table 4-1. The address map is also illustrated in Figure 4-1 for the VSB operating in "bounce" mode, and in Figure 4-2 for the VSB operating in "non-bounce" mode. Refer to section 4.2.9 for a description of bounce operation.

The bottom half of the address map ( $\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset$  to 7FFFFFF) is decoded for cacheable resources, and the top half of the address map ( $\vartheta\emptyset\emptyset\emptyset\emptyset\emptyset\emptyset$  to FFFFFFF) is decoded for noncacheable resources. The top 256kb of the address map (Fxxxxxx) are further decoded for special VMEbus (A24,A16,D16) resources and for local (on-board) resources. The local resources and VMEbus Short I/O (A16) resources are decoded in the top megabyte (FFFxxxxx) of this address space. Some of the resources in the address map appear replicated throughout a larger address space. For these cases, the recommended address range to use is given in Table 4-1, and the replicated address ranges should not be used. All of the address references are given as physical addresses outside the MC68030 chip (output side of the PMMU). The resources of the address map are described in the following sections.

#### 4.2.1 Function Codes

The three function code signals on the MC68Ø3Ø specify the type of cycle being run. They specify User Data (FC=1), User Program (FC=2), Supervisor Data (FC=5), and Supervisor Program (FC=6) cycle types, as well as three reserved cycle types (FC=Ø,3,4) and CPU Space cycles (FC=7). Processor cycles using any of the non-CPU Space cycle function codes (FC=Ø-6) will select the resources of the address map illustrated on the left in Figure 4-1 and Figure 4-2. Processor cycles using the CPU Space cycle function code (FC=7) will select an alternate address map containing the MC68882 coprocessor and the interrupt acknowledge vectors as shown on the right in Figure 4-1 and Figure 4-2.

The function codes are usually generated automatically by the  $MC68\emptyset3\emptyset$ , and not directly specified by the user. However, the user can directly specify the function codes for data accesses with the MOVES instruction. Caution should be used if doing this to a device over VMEbus as the lower three bits of the VMEbus address modifiers

| Address                                                     | Resource                                         | Size         | Comments                                       |

|-------------------------------------------------------------|--------------------------------------------------|--------------|------------------------------------------------|

| FFFFØØØØ-FFFFFFFF<br>FFFCØØØØ-FFFEFFFF                      | VSB/VMEbus-SHIO<br>(Reserved)                    | 64K          | A16, D16, CI<br>VSB/VMESHIO replicated         |

| FFFBØØ3Ø-FFFBFFFF<br>FFFBØØØØ-FFFBØØ2F                      | (Reserved)<br>VMEchip CSR                        | 48           | VMEchip CSR replicated D16 (odd byte only), CI |

| FFFAØØØ8-FFFAFFFF<br>FFFAØØØØ-FFFAØØØ7                      | (Reserved)<br>VSBchip CSR                        | -<br>8       | VSB/VME<br>D32, CI                             |

| FFF9ØØØØ-FFF9FFFF                                           | (Reserved)                                       | -            | Local Timeout                                  |

| FFF8ØØØØ-FFF8FFFF                                           | (Reserved)                                       | -            | VSB/VME                                        |

| FFF7ØØ1Ø-FFF7FFFF<br>FFF7ØØØØ-FFF7ØØØF                      | (Reserved)<br>DUART                              | 16           | DUART replicated D8, CI                        |

| FFF6ØØ2Ø-FFF6FFFF<br>FFF6ØØØØ-FFF6ØØ1F                      | (Reserved)<br>PI/T-Local CSR                     | 32           | PI/T replicated<br>D8,CI                       |

| FFF5Ø8ØØ-FFF5FFFF<br>FFF5Ø7F8-FFF5Ø7FF<br>FFF5ØØØØ-FFF5Ø7F7 | (Reserved)<br>Time-Of-Day Clock<br>NV Static RAM | 8<br>2Ø4Ø    | NVRAM/TOD replicated<br>D8,CI<br>D8,CI         |

| FFF48ØØØ-FFF4FFFF<br>FFF4ØØØØ-FFF47FFF                      | (Reserved)<br>Static RAM                         | 32K          | SRAM replicated<br>D8, CI                      |

| FFF2ØØØØ-FFF3FFFF<br>FFFØØØØØ-FFF1FFFF                      | (EPROM Expansion)<br>EPROM                       | 128K<br>128K | 1M bit EPROM option<br>D16, CI, LTO on writes  |

| F1ØØØØØØ-FFEFFFFF                                           | VSB/VMEbus                                       | 239M         | A32, D16, CI                                   |

| FØØØØØØØ-FØFFFFFF                                           | VSB/VMEbus                                       | 16M          | A24, D16, CI                                   |

| 8ØØØØØØØ-EFFFFFFF                                           | VSB/VMEbus                                       | 1792M        | A32, D32, CI                                   |

| Ø1ØØØØØØ-7FFFFFFF                                           | VSB/VMEbus                                       | 2Ø32M        | A32, D32, CCB                                  |

| ØØØØØØØØ-ØØFFFFFF                                           | VSB/VMEbus                                       | 16M          | A32, D32, CCB<br>or A24, D32, CCB              |

TABLE 4-1. ADDRESS MAP

Notes: CCB = Cacheable, CI = Cache Inhibited A24 option at ADR = Ø is selected by the PI/T CSR bit VA24. All VSB references are A32.

FIGURE 4-1. MVME141 SYSTEM ADDRESS MAP (WITH VSB BOUNCE ENABLED)

FIGURE 4-2. MVME141 SYSTEM ADDRESS MAP (WITH VSB BOUNCE DISABLED) 4-4 are generated directly from the function codes through the VMEchip. This may generate a reserved address modifier on VMEbus that the target device may not respond to. Refer to the VMEbus Specification for address modifier usage.

#### 4.2.1.1 CPU Space Address Map

Processor cycles using the CPU Space function code (FC=7) will select an alternate address map containing the MC68882 Floating Point Coprocessor (FPC) and the interrupt acknowledge vectors. The FPC is decoded as coprocessor #1 and is selected automatically by the processor when CPID equals 1 in the coprocessor instructions. The interrupt acknowledge vectors are accessed automatically by the processor during interrupt acknowledge cycles. The CPU Space address map is illustrated in Figure 4-1 and Figure 4-2. Only certain address bits are decoded to select the CPU Space resources. The FPC appears normally at space addresses 22000 through 2201F, and the interrupt acknowledge vectors appear normally at space address that does not select the FPC or interrupt vectors will be routed to the VSB bus but not to VMEbus. The CPU Space addresses are usually generated automatically by the processor, and not directly space addressing.

### 4.2.2 EPROM

The EPROM is decoded starting at address FFFØØØØØ. It is either 128Kb or 256Kb in size depending on whether 64K x 8 or 128K x 8 EPROMs are installed. The EPROM is configured as a 16-bit wide (D16), cache inhibited (CI) data port for the processor. It is a read-only resource, and any write access to the EPROM address space will be terminated with a local bus timeout (LTO). The EPROM is automatically selected after any power-up or reset condition to supply the initial stack pointer and program counter to the processor. It will subsequently remain selected until an access to any on-board address is performed.

### 4.2.3 Static RAM

The local static RAM (SRAM) is decoded at addresses FFF40000 through FFF47FFF. It is 32Kb in size, and it is configured as an 8-bit wide (D8), cache inhibited (CI) data port for the processor. The static RAM is decoded at sequential byte addresses, and it is accessible with byte, word, or longword operations. The static RAM is not accessible from VSB or VMEbus.

### 4.2.4 NVRAM/Time-Of Day Clock

The combination nonvolatile RAM and Time-Of-Day clock (NVRAM/TOD) chip is decoded at addresses FFF500000 through FFF507FF. It is 2Kb in size, and it is configured as an 8-bit wide (D8), cache inhibited (CI) data port for the processor. The NVRAM/TOD is decoded at sequential byte addresses, and it can be accessed with byte, word, or longword operations. The NVRAM and time-of-day clock are battery backed-up for continuous data retention and clock operation. After power-up, the first write operation to the NVRAM must be used to test the condition of the battery. If the first write is unsuccessful, then the battery voltage is low and the NVRAM/TOD chip should be replaced to ensure nonvolatile operation.

The registers for the time-of-day clock are accessed through the top 8 bytes of the 2Kb NVRAM/TOD address space. The registers are summarized in Table 4-2.

| Address  |    |    |    | Da | ta |    |    |    | Function        |

|----------|----|----|----|----|----|----|----|----|-----------------|

|          | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DØ | <br>            |

| FFF5Ø7F8 | W  | R  | S  | Ca | Ca | Ca | Ca | Ca | Control         |

| FFF5Ø7F9 | ST | -  | -  | -  | -  | -  | -  | -  | Seconds (ØØ-59) |

| FFF5Ø7FA | ø  | -  | -  | -  | -  | -  | -  | -  | Minutes (ØØ-59) |

| FFF5Ø7FB | KS | ø  | -  | -  | -  | -  | -  | -  | Hour (ØØ-23)    |

| FFF5Ø7FC | ø  | FT | ø  | ø  | ø  | -  | -  | -  | Day (Ø1-Ø7)     |

| FFF5Ø7FD | ø  | ø  | -  | -  | -  | -  | -  | -  | Date (Ø1-31)    |

| FFF5Ø7FE | ø  | ø  | ø  | -  | -  | -  | -  | -  | Month (Ø1-12)   |

| FFF5Ø7FF | -  | -  | -  | -  | -  | -  | -  | -  | Year (ØØ-99)    |

|          |    |    |    |    |    |    |    |    |                 |

TABLE 4-2. NVRAM/TOD CLOCK REGISTER MAP

Notes: W = Write bit, R = Read bit

S = Calibration Sign bit, Ca = Calibration value (5 bits) ST = Stop bit, KS = Kick Start, FT = Frequency Test

Setting the "R" bit (R=1) in the TOD control register will latch the current time from the clock in the other TOD registers for reading. Clearing the "R" bit (R=Ø) will enable the continual updating of the TOD registers by the clock with the current time. Setting the "W" bit (W=1) in the TOD control register will enable writing of the other TOD registers by the processor to change the current time. Clearing the "W" bit (W=Ø) will set the clock to the time that was written in the registers. The KS, FT, and zero (Ø) bits in the TOD registers must be written as zero to allow normal clock operation. The 5-bit calibration value (Ca) and the calibration sign bit (S) 4-6

can be used to speed up or slow down the clock at a linear rate of approximately 5.35 seconds per month per increment. The time values are encoded in BCD format. Refer to the Thomson/Mostek MK48TØ2 data sheet for a detailed operating description of the NVRAM/TOD clock chip.

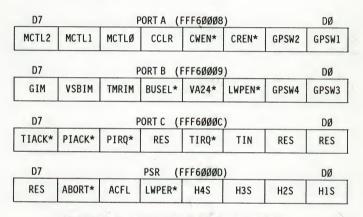

### 4.2.5 Parallel Interface/Timer (PI/T)

The PI/T (MC6823Ø) is decoded at addresses FFF6ØØØØ through FFF6ØØ1F. It is 32 bytes in size, and it is configured as an 8-bit wide (D8), cache inhibited (CI) data port for the processor. The registers of the PI/T are decoded at sequential byte addresses, and they can be accessed with byte, word, or longword operations (with the exception of certain board-defined control bits in the Port A and Port B data registers). The register assignments are summarized in Table 4-3.

The PI/T consists of two logically independent sections: the parallel ports and the counter/timer. The parallel ports are dedicated to the MVME141 hardware, and they must must be properly configured by the user to operate the board. The parallel ports are described in the following section. The counter/timer is not dedicated by the hardware and is available for general user applications. The counter/timer can be operated from the 8MHz clock source of the PI/T chip, or from the counter/timer output pin OP3 of the DUART chip. The PI/T is reset by any power-up or reset condition. Refer to the PI/T User's Manual for a detailed operating description of the PI/T chip.

# 4.2.5.1 PI/T Port Configuration

The parallel port section of the PI/T is used on the MVME141 for control and status registers (CSRs) and for interrupt control. It must be properly configured to support the board.